先进封装,在此一举

当我们站在2023这个节点谈论芯片性能之时,大家仿佛已经达成了共识,先进制程不再是提高性能的关键,每两年把芯片晶体管密度提升一倍已经变得极为困难,不论是台积电,或是三星,再或是英特尔,把制程往前推进1nm都要消耗比过往数倍乃至十几倍的投入,简而言之,先进制程,越来越不划算了。

此时先进封装开始崭露头角,以苹果和台积电为代表,开启了一场新的革命,其主要分为两大类,一种是基于XY平面延伸的先进封装技术,主要通过RDL进行信号的延伸和互连;第二种则是基于Z轴延伸的先进封装技术,主要通过TSV进行信号延伸和互连。

前者为2D先进封装,代表为FOWLP和FOPLP等,而后者即为3D封装,代表为SoIC和Foveros等,目前还有兼具两种封装特点的2.5D封装,代表为CoWoS和EMIB等。

目前3D 封装大多应用于提升HPC 芯片的性能,常见于HBM与CPU、GPU、FPGA、或NPU 等处理器彼此间的芯片整合。

如台积电提出的SoIC 整合封装架构,其主要利用W2W 及C2W 的混合键合技术,实现10um 以下I/O 节点互连、减少寄生效应、并使芯片更薄等优势。

三星则于2020 年推出名为X-Cube 的3D 封装技术,将4 颗SRAM 堆叠在逻辑核心运算芯片上,并通过TSV 结构进行连接。

英特尔于2018 年底推出名为Foveros的3D 逻辑芯片封装技术,通过TSV 与Micro Bumps 将不同芯片以Face-to-Face 方式堆叠连接,目前Foveros 技术能使凸点间距达到50um,未来有望缩减到10um,让凸点数量达到每平方毫米10,000 个。

在这几种封装方式里,其主要目的都是将不同类型的芯片,通过3D立体堆叠的形式整合在一起,从而实现高性能、小体积、低耗电等目标优势,也即异构集成。

混合键合革命

封装中最早采用的引线键合(Wire Bonding),由于其接点仅能以周列形式排列在芯片周围,接点的I/O 数量有限,而IBM 提出的倒装接合(Flip Chip Bonding),利用焊锡微凸块(Solder Bump)当作接点将芯片与芯片接合在一起,接点为阵列式排列,可以分布于整个芯片上,可以提高接点I/O 数量,不过这项技术在 50μm 或 40μm 的间距时表现尚可,人们很快发现,这种方式由于热膨胀不匹配,会出现翘曲和芯片移位。

事实上,微凸块一旦做到 10 微米以下的间距时,暴露的问题就愈发增多,当凸块结构较大时,电镀微凸块高度的极小不均匀性或回流焊过程中的变化可能可以忽略不计,但对于细间距微凸块,这些微小的变化可能会导致接合处形成不良,并影响电气良率,最终导致晶粒和封装出现缺陷。

铜─铜混合键合(Cu-Cu Hybrid Bonding)技术应运而生,将金属接点镶嵌在介电材料(Dielectric Material)之间,并同时利用热处理接合两种材料,利用铜金属在固态时的原子扩散来达到接合,故不会有Bridging 问题。铜制程是半导体业非常成熟的技术,铜─铜接点的间距可以微缩到10μm以下,因此在1×1cm² 的晶片内,能够制作出超过一百万的接点,因此金属的直接接合变得非常重要。

混合键合此前在业界通常被称为DBI(Direct Bond Interconnect,直接键合),20世纪80年代中期,Paul Enquist,Q.Y. Tong和Gill Fountain在三角研究所(RTI)的实验室首次提出了这一技术,2000年,三人成立了Ziptronix公司,并于2005年推出了一种称为低温直接键合互连 (DBI) 的技术,这是混合键合的第一个版本。

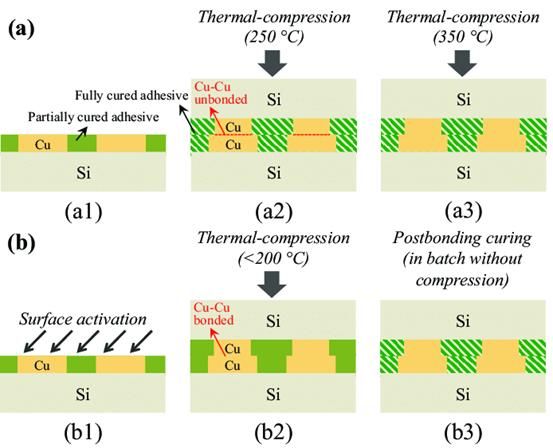

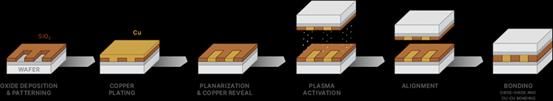

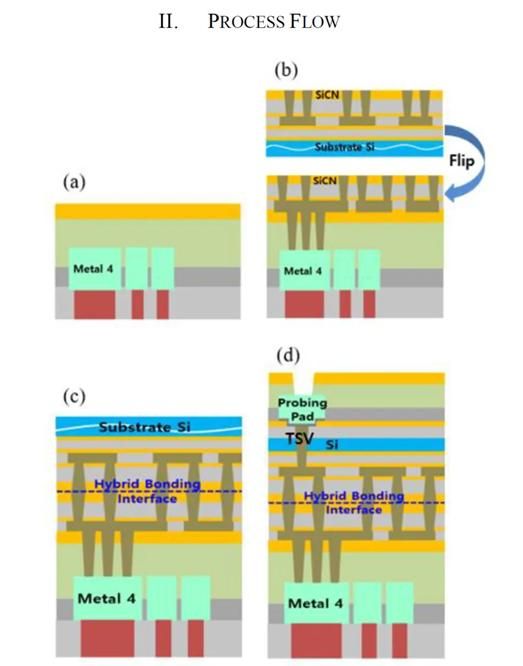

它验证了低温直接键合(Direct Bond Interconnection, DBI)的可行性,首先准备好晶片具有SiO 2(介电材料)与铜(接点金属),此时铜部分将会有点略低于介电材料厚度,利用电浆(Plasma)做表面活化处理,将晶片面对面在室温下进行对位接合,由于凡德瓦力作用已具有一定的接合强度,接着在100℃ 下持温让SiO 2与SiO 2之间进行缩合反应,形成强力共价键提高接合强度 。接着再将温度提高到300℃ 至400℃ 持温,此时由于铜金属的热膨胀系数较SiO 2来的大,铜表面将会碰触在一起,并自然受到一压应力,促使铜接点进行扩散接合。

有研究学者指出,想要达到低温键合,介电材料层与金属层在经过化学抛光研磨后造成的高度差异将会是关键,研磨液与研磨参数的选择是导致不同厚度的主因,厚度差越小,便可于较低温度使铜表面接触并开始进行接合。

混合键合与倒装接合比,它带来了三大新优势,第一为可以达到超细间距与超小接点尺寸,实现更高I/O 数量;第二,由介电材料接合取代底部填充剂,进一步节省填充成本;第三,倒装技术会让芯片与基板或芯片片间存在约10 至30 μm的厚度,而混合键合几乎没有厚度,在多层堆叠的情况下可以大幅减少总体厚度。

目前铜─铜混合键合主要分为了三种方式,分别为最常见的晶圆到晶圆(W2W)工艺,芯片到晶圆(D2W)和芯片到晶圆(C2W)工艺,后两种工艺目前还在研发当中。

其中,W2W 虽然已经实现量产,但它对于上下芯片的大小限制须为一样大小,否则将有区域浪费;D2W是将切割好的Die用临时键合的方式粘到晶圆上,然后整片地和另一片产品晶圆整片键合再解键,这项技术容易累计误差,且成本高,对Die的厚度变化范围也有较高要求;C2W将切好的Die分别放置晶圆的对应位置上,位置精度虽然提高且厚度变化要求不在严苛,但颗粒控制也是影响它继续普及的问题。

2015年,发明混合键合技术的Ziptronix被Xperi收购,2019年,Xperi 完成了混合键合技术的最终专利布局,而在此之前,这项技术已经授权给了包括索尼在内的多家厂商。

从20世纪80年代的构想,到2005年的初步验证,再到2015年之后的技术授权,混合键合历经三十余年,终于为先进封装铺平了道路,解决了芯片厂商对封装未来的最大疑虑,此后混合键合领域更是呈现出了一篇千帆竞逐的景象。

群雄决战封装

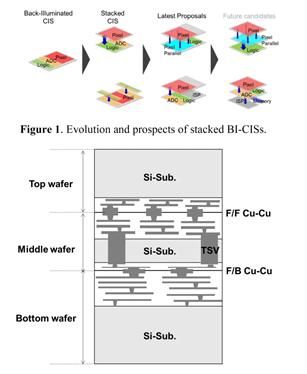

2016 年,索尼首先将混合键合技术应用在三星Galaxy S7 的背照式CMOS 影像传感器(Backside-illuminated CMOS Image Sensor, BI-CIS)中,大幅提高了镜头解析度。目前索尼每年出货数百万个采用 6.3 微米间距混合键合技术的 CMOS 图像传感器,并堆叠了 3 个芯片,而其他公司采用的间距密度要低得多,出货量也要小得多。

作为这项技术的急先锋,索尼在2022年展示了 1 微米间距的面对面混合键合和 1.4 微米的背对背混合键合,而它之所以如此激进,就是希望通过这项技术继续分解和堆叠图像传感器像素的功能,以此捕捉更多光线和数据,将其转化为实际的照片和视频。

SK海力士最早将于2025年量产混合键合,并准备将其用于HBM4产品,与现有工艺相比,混合键合提高了散热效率并减少了布线长度,从而实现了更高的输入/输出密度,能够把当前的最大12层堆叠增加到 16 层。而SK 海力士 PKG 技术开发负责人Ki-il Moon 表示:“我们正在专注于该技术的开发(与混合键合相关),并且实际上已经获得了有意义的产量,该技术将于2025~2026年实现商业化。”

三星在2020年8月,就对外展示了其自己的3D封装技术——X-Cube,全称为“eXtended-Cube”,将SRAM层堆叠在逻辑层之上,允许多层超薄堆叠,其表示三星代工厂正在开发超细间距铜-铜混合键合,其已经实现了小于 4微米的间距。

英特尔在2022年12月的IEEE国际电子器件会议上,宣布了全新的混合键合技术,gaijishu将互连间距继续微缩到3微米,英特尔实现了与单片式系统级芯片(system-on-chip)连接相似的互连密度和带宽,与IEDM 2021上公布的成果相比,英特尔在IEDM 2022上展示的最新混合键合技术将功率密度和性能又提升了10倍。

此外,2002年6月,CEA-Leti 和英特尔宣布了一种全新的混合键合自对准工艺,使用水滴的毛细力(capillary forces)来对齐目标wafer上的die,该工艺有可能增加校准精度以及每小时数千个芯片的制造吞吐量,采用取放工具后键合的最先进的对准是 1µm,最好的情况是 700nm,而新工艺提供低于 500nm 甚至小于 200nm 的后键合对准。

imec高级研究员、研发副总裁兼3D系统集成项目主任Eric Beyne在IEDM的一篇论文中表示,目前imec的研究已经证明了在7微米间距实现混合键合的可行性。imec官方表示,利用这项技术,芯片之间或芯片与硅中介层之间的 3D 互连密度比现有技术高出十六倍以上其开发间距小至3μm且具有高公差拾放精度的芯片间混合键合。

台积电无疑是混合键合的集大成者,其SoIC 封装技术依靠混合键合,在芯片 I/O 上实现了强大的接合间距可扩展性,实现了高密度的芯片到芯片互连,其键合间距从 10 微米以下开始,台积电表示与目前业界最先进的封装解决方案相比,短芯片到芯片连接具有外形尺寸更小、带宽更高、电源完整性和信号完整性更好以及功耗更低的优点。此前,台积电已经展示了其第四代混合键合技术的研究成果,该技术可实现每平方毫米 100,000 个接点数量。

2021年底,AMD介绍了他们在服务器处理器上已采用的台积电混合键合技术,2022 年初,AMD宣布Ryzen 7 5800X3D 也采用了Hybrid Bonding 技术,将7nm SRAM 叠接在7nm 处理器之上,铜─铜混合键合能提升200 倍的接点密度,而且每个讯号传递所需的能量降低至三分之一以下。

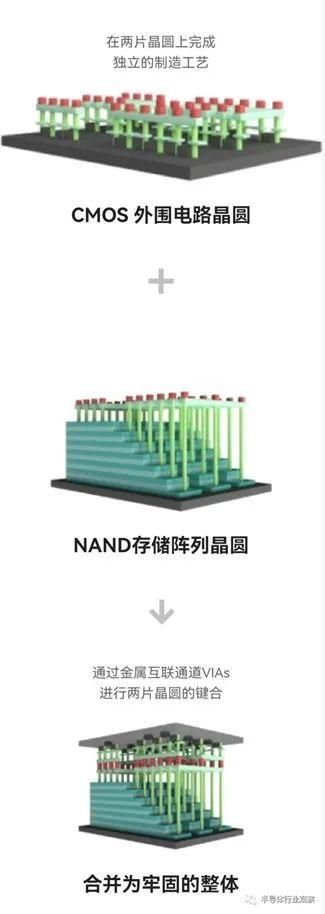

值得一提的是,国内的长江存储所推出的Xtacking架构,即采用了W2W的混合键合技术,利用不同的工艺,先后制作Memory晶圆和CMOS晶圆,在后道制程中构建两者的触点。通过混合键合,这些触点被链接导通,Memory和CMOS在垂直方向实现了互联。

长江存储官方表示,混合键合在3D NAND闪存上实现数十亿根金属通道的连接,随着层数的不断增高,基于晶栈Xtacking所研发制造的3D NAND闪存将更具成本和创新优势。

针对这一项新兴技术,设备厂商们也未能置身事外,混合键合作为一项后道工艺,其设备主要由德国的苏斯(Karl Suss)和奥地利的EVG(EV Group)所提供,日本的佳能和三菱目前也有意发展该键合设备,但目前市占率和技术水平还和欧洲厂商有一定差距。

混合键合即是未来?

对于混合键合技术来说,目前最大的应用方式依旧是以索尼为代表的堆栈式CIS,经过数年的优化后,目前CIS领域在利用这项工艺时可谓是得心应手,未来也有望实现更大规模的量产。

而第二大应用领域无疑是DRAM和NAND,我们可以看到三星、海力士和长江存储等在这方面的积极布局,部分厂商已经拿出了一定成果,可能在2025年,我们就能见到混合键合技术在该领域的量产落地。

而最后的应用场景即以台积电的SoIC技术为代表的3D先进封装,目前在AMD处理器上已经实现量产,未来苹果也有望在MacBook所搭载的M系列处理器上采用这一技术,其大规模投产可能也会在2025年左右。

芯片提升性能以往看制程,如今看封装,封装看向异构集成,而异构集成的过往难点就是键合,如今铜─铜混合键合日趋成熟,背后环环相扣的工艺就有望实现芯片性能的下一步飞跃,我们深信这一天已不再遥远。

参考来源

1. 3D IC封裝:超高密度銅-銅異質接合——matek

2. Hybrid Bonding takes Heterogeneous Integration to the Next Level——3dincites

3. Packaging Developments From ECTC 2022——semianalysis

发布于:上海

相关推荐

先进封装,在此一举

先进封装大战打响

先进封装,格局生变

先进封装,拼什么?

先进封装,关注什么?

先进封装,对半导体产业链有多重要?

台媒:先进封装产能,被疯抢

持续采购先进EDA工具,联电发力先进封装

英特尔先进封装产能扩大4倍,准备单独接单

先进封装,台积电的另一把尖刀

网址: 先进封装,在此一举 http://m.xishuta.com/newsview92963.html