先进封装,台积电的另一把尖刀

本文来自微信公众号:远川研究所 (ID:caijingyanjiu),作者:何律衡,题图来自:视觉中国

2023年6月,苹果Apple Silicon最后一块拼图归位:新款Mac Pro换上M2 Ultra,英特尔彻底从苹果的Mac产品线消失。承担这一历史转折点的M2 Ultra,成为半导体产业关注的焦点:

这颗苹果有史以来面积最大的SoC,由两颗M2 Max芯片“缝合”而成,晶体管数量直接翻倍,达到了1340亿颗——作为对比,英伟达的RTX4090拥有763亿个晶体管,H100为800亿。

这块芯片背后,是一个名为UltraFusion的“缝合技术”。

当摩尔定律失效成为业内共识,制程提升的成本指数级飙升,提高制程已不再是高性能芯片增加晶体管数量的最佳选择。将两块芯片合二为一虽然听起来简单粗暴,但在苹果之前,失败的尝试不在少数。

此前,几乎所有的“缝合”方案,都无法解决芯片在连接过程中产生的损耗,使得性能往往“1+1<2”。而M2 Ultra却突破了这一天堑,实现了真正的1+1=2。

UltraFusion背后的功臣并不难猜,正是当前先进封装产能供不应求的台积电。

当业内还在热议英特尔修改命名缩短与台积电的差距,又或是台积电和三星谁将率先突破2nm时,台积电却早已凭借先进封装,走在竞争对手的前面,为灯枯油尽的摩尔定律续命。

为了实现这个1+1=2,台积电走了20年。

停滞20年的间距

2005年,伴随芯片制程迈入65nm大关,台积电在全球芯片代工市场中拿下了50%的份额,身后的竞争者似乎只剩下了苦苦追赶的三星,感觉大势已定的张忠谋宣布卸任CEO,退居二线,但时任台积电技术总裁蒋尚义却在思考一个问题:

过去十五年,芯片制程紧跟摩尔定律的路线图,从600nm一路狂奔到了65nm。但芯片之间封装的金属间距(Metal Pitch)却停留在110um,已经20年没有进步。

何为金属间距——一般我们拿到手的芯片(如CPU),其实是一个完整的芯片模组。严格意义上的芯片,是从晶圆上切割下来的裸片(Die)。

按照传统封装的步骤,需要将这些裸片放到基板(Sustrate)上,引出管脚/引线,再将其固定、封装进一个外壳中,才能应用于实际的电路中。

蒋尚义思考的金属间距,其实就是图中引线的间距,比如CPU和内存交换数据,就是依靠这些引线。理论上来说,引线数量越多,不同芯片间的连接效率就越高,整体性能也就越好。但由于引线是金属材质,一旦密度提升,功耗和发热也会越高。

在这个背景下,蒋尚义构想了一个大胆的方案:与其冒险增加引线的密度,不如把两块芯片封装在一个硅片上,由于物理距离更近,电信号传输中的延迟问题得到改善,金属材质带来的弊病也迎刃而解。

从“先封再拼”转变为“先拼再封”,前者如今被归类为传统封装,后者则是近几年大热的概念——“先进封装”。

但在当时,蒋尚义的构想在技术上过于大胆,而且缺乏商业上的可行性。

所谓摩尔定律,就是指每隔18-24个月,芯片上可容纳晶体管数量翻一番。几十年里,半导体产业遵照摩尔定律快速发展,从130nm到90nm,从65nm到40nm,仿佛游戏过关一样顺畅。

对于代工厂来说,相比芯片制程带来的性能提升,重金投入先进封装带来的性能进步,实在是性价比过低。加上蒋尚义在2006年就跟随张忠谋一起退休,先进封装方案并没有付诸实施。

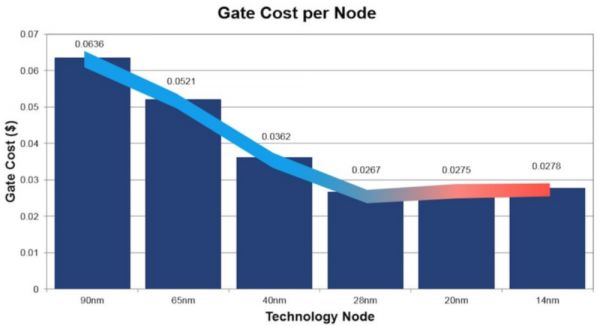

但到了2009年,业内上下开始攻克28nm制程,工程师们才意识到了问题的严重性:晶体管单位制造成本不降反升,制程升级提升性能的性价比开始降低。

换句话说,摩尔定律正在失效。

28nm->20nm->14nm,晶体管单位制造成本上升;图源:IBS

同一时期,依靠移动终端市场的红利,三星从微不足道的竞争者迅速成长为台积电最大的竞争对手。

金融危机期间,中国台湾地区的面板和内存产业被三星的反周期屠刀相继斩落马下,击垮当时利润大幅下滑台积电并非没有可能。

2009年,张忠谋重新出山,并请回了已经退休的蒋尚义,希望后者带领台积电领先于业内实现28nm制程量产,重现130nm超越IBM的辉煌,并借此关键制程,搭上移动终端的末班车。

蒋尚义的回归,使得台积电两年后以“后闸级”技术路线成功超越三星率先量产28nm,而真正让台积电赢在了起跑线上的,是其回归时与“晶体管领先”一同向张忠谋提出的“先进封装”计划。

28nm制程,是摩尔定律死亡倒计时的开始,也是台积电先进封装的起点。

昂贵的进步

2009年,在张忠谋的首肯下,蒋尚义带着1亿美元的设备投资金和400多人的工程师团队,开始了先进封装技术的研发。但业内对台积电进军先进封装的反应却大多悲观。

半导体产业分为上游设计、中游制造、下游封装,封装环节技术长期进步缓慢,利润被摊薄,大多走薄利多销路线,台积电作为代工厂天然人工成本更高,在与封装厂的价格战中自然不具备优势。

另外,与同样“半路出家”研发先进封装的英特尔、三星相比,台积电的技术水平同样落后。例如当时引起关注的“扇出型晶圆级封装”,英特尔、三星分列专利数第二、三位,台积电甚至没进前十。

台积电的首个先进封装技术CoWoS,便是在这种氛围下诞生的。

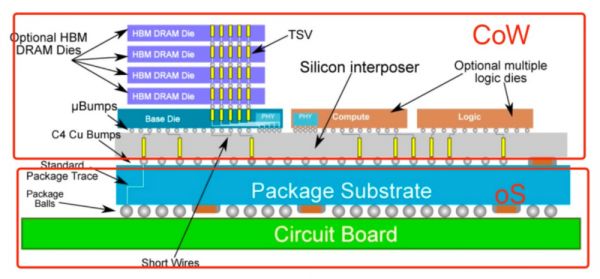

CoWoS由CoW和oS组合而来:CoW表示Chip on Wafer,指裸片在晶圆上被拼装的过程,oS表示on Substrate,指在基板上被封装的过程——这也是蒋尚义在2006年提出的构想。

与其他类似的技术相比,台积电CoWoS的突出优势体现在连接裸片的方式:装载裸片的晶圆被台积电称为硅中介层,在硅中介层中,使用微凸块(ubmps)、重新布线(RDL)等技术,代替了传统引线键合用于裸片间连接,大大提高了互联密度以及数据传输带宽。

然而,初生的CoWoS一度处境尴尬。2011年,台积电得到FPGA大厂赛灵思订单,凭借CoWoS以及共同开发的硅通孔(TSV)等技术,成功将4个28nm FPGA芯片拼接在一起,推出了史上最大的FPGA芯片。

但这也是整个2011年,台积电先进封装项目组收到的唯一订单。

每个月50片晶圆的订单量,相对于烧掉几千片废片的研发投入来说,可谓杯水车薪,这是蒋尚义和台积电都没有想到的局面。

随后,台积电又找到了合作多年的亲密战友英伟达——由于GPU计算时需要频繁与内存通信,获取和存储数据,对延迟的容忍度更低,对带宽需求也更高。

因此,英伟达是蒋尚义在开发CoWoS时就确定的目标客户之一,但没想到英伟达同样意兴阑珊。

在一次与高通高管的午餐中,蒋尚义得到了一个意料之中的答案:CoWoS太贵了。

“我只愿意为这个技术花费1美分/平方毫米。”带着这句话,蒋尚义找到余振华,得到CoWoS目前的价格在7美分/平方毫米的回答,确认了这6倍的差距便是客户犹豫的原因。

如此大的成本差距,势必无法短时间内通过技术消弭。台积电决定给CoWoS做“减法”,开发廉价版的CoWoS技术。制造、封装经验丰富的余振华,很快交出了替代方案——InFO。

CoWoS技术之所以费钱,主要是由于硅中介层,其本质就是一片硅晶圆,还要在中间布线做连接,自然成本高昂。而InFO把硅中介层换成了其他材料,牺牲了连接密度,却换来了成本的大幅下降。

紧接着,台积电找到了那个位于美国西海岸,可以靠一己之力改变供应商命运的超级甲方:苹果。

苹果把单买了

2009年,三星决策层制定了一个秘密计划,李在镕准备利用金融危机彻底打垮中国台湾地区的电子产业,先打面板,再打内存,最后打垮台积电,让三星完全主宰东亚电子产业。

这个计划一度非常顺利,到2014年,中国台湾地区的面板和内存奄奄一息,台积电同样风雨飘摇——依靠从台积电挖来的梁孟松,三星率先量产14nm FinFET工艺,台积电的技术优势几乎一夜之间被抹平了。

技术落后最直接的打击体现在大客户订单。有先进制程打底,三星还凭借独家PoP封装技术,将内存芯片直接堆叠在SoC上方,从而大大减小了芯片面积,赢得了苹果自研移动SoC——A系列的超级大单。

对于移动SoC来说,由于设备大小的限制,加上大部分空间还要留给电池,对芯片的要求既有性能,还需要把芯片尽可能做小。

然而,从开始自研的A4到A9,从45nm到16nm,苹果发现,依靠制程升级缩小芯片越来越不具备性价比。三星的PoP封装方案,成为了在不升级制程的情况下,缩小芯片面积的最优解。

但与此同时,三星手机正在全球市场攻城略地,成为了苹果最大的竞争对手。2013年前后,苹果一边和三星打官司,一边把芯片订单向台积电倾斜。

在此背景下,缩小芯片效果和性价比都超越PoP封装的InFO,成为了台积电“被扶正”的转机。

2016年,搭载苹果最新A10移动SoC的iPhone 7上市,全部由台积电代工。在CPU速度较前代iPhone 6提高两倍多、内存容量提高一倍的情况下,机身厚度控制在了7.1毫米,是历代iPhone中第二薄的。

最重要的是,以上所有成就,均是在没有升级制程的情况下达成的。

有了苹果先行先试,曾因为价格问题迟疑不定的芯片大厂们终于放心大胆地上了车,英伟达、AMD、谷歌,甚至竞争对手英特尔,都在自家高性能芯片上用上了CoWoS封装。

2023年,AI芯片水涨船高,英伟达GPU对CoWoS的需求从年初预估的3万片暴涨至4.5万片,不得不提前加单。

然而,先进封装像潘多拉的盒子,多米诺骨牌效应才刚刚开始。半导体产业花费了几十年稳定下来的上下游分工模式,正在被缓慢松动。

中国大陆走到哪儿了?

长期以来,封装测试环节都是芯片产业链的底端,因此很早就从日韩向中国大陆转移。近十年来,封测已经成为中国大陆发展最快、目前最具优势的环节。

而当晶圆制造环节由于众所周知的原因,难以向14nm以下再进一步时,先进封装的出现,也一度被视为弯道超车的秘籍。

事实上,中国大陆的头部厂商在先进封装的开发上也并不落后。例如全球第三、中国大陆第一的封测厂长电科技,已经开发了2.5D/3D封装、晶圆级封装(WLP)、堆叠封装(PoP)等先进封装技术,覆盖面可追平日月光。

全球第五、中国大陆第二的通富微电,除了掌握2.5D/3D封装等技术外,还在收购了AMD两大封测厂后与其深度绑定,后者是目前先进封装的最大客户之一。

但有别于传统封装,先进封装固然提高了封测环节的附加值,但同样需要上游环节的配合。简单来说,传统封装的流程是晶圆厂将制造完成的芯片交由封测厂封装,彼此独立。

先进封装需要芯片设计公司、晶圆厂和封测厂在芯片设计阶段,就开始定制和研发制造工艺,联系更加紧密。

正是因为先进封装的关键技术需要芯片设计公司推动,在芯片制造层面实现,因此代工厂先天比封测厂更有优势,也被认为是最主要的玩家。封测厂更多承接技术难度低、靠近后道封装的部分。比如,台积电就将CoWoS的oS外包给了日月光。

中国大陆封测厂的弱势在于,由于工艺制程落后,代工厂本身就没有多少先进封装的订单,芯片设计公司提供的订单就更少了。

台积电的先进封装工艺拔地而起,是因为有苹果这个超级甲方的存在。理论上来说,海思可以扮演这个角色,但在因制裁而无法做先进芯片设计后,缺少了关键的推动者,中国大陆先进封装一度发展困难。

这就导致先进封装风口已现,但承担了全球封测近20%产能的中国大陆,却迟迟等不来指引航向的掌舵者。始于2018年的制裁,对半导体产业的影响,或许比预期中的还要深远。

参考资料

[1] 蒋尚义2022年3月采访速记,美国计算机历史博物馆

[2] 台积电的先进封装是这样炼成的,《天下杂志》

[3] 扶摇直上:台积电崛起之路,1973手机馆

[4] 苹果与台积电,过去十年最成功的芯片“搭档”?半导体行业观察

[5] 苹果iPhone 7 A10处理器的新封装在技术和商业上都产生了巨大的影响,Yole Department

[6] 先进封装第二部分:英特尔、台积电、三星、AMD、日月光、索尼、美光、SKHynix、YMTC、特斯拉和英伟达的选项/使用回顾,Semianalysis

[7] 微观视角看AI芯片,macropolo

[8] 苹果官网M系列芯片介绍

[9] 台积电官网3D Fabric介绍

本文来自微信公众号:远川研究所 (ID:caijingyanjiu),作者:何律衡

相关推荐

台积电 vs 英特尔 vs 三星:决战半导体3D封装

先进封装大战打响

先进封装,格局生变

历史潮头上的台积电:两堵高墙,一柄尖刀

台积电回应CoWos封装产能扩充传闻:仍在评估中

台积电攻防战

台积电登顶的三个节点

华为7亿美元紧急下单台积电?先进制程工艺不容乐观

干脆台积电改叫“苹积电”得了

苹果与台积电,过去十年最成功的芯片“搭档”?

网址: 先进封装,台积电的另一把尖刀 http://m.xishuta.com/newsview81166.html