台积电,颠覆封装?

过去几年,人工智能彻底带火了GPU,而作为背后的支撑力量。台积电CoWoS封装技术也强势崛起。

众所周知,多年来,GPU绝对龙头英伟达一直是台积电的重要合作伙伴,但在 AI 领域最初的热潮之后,NVIDIA 更进一步深化了与台积电的合作。如今,双方的合作关系已经发展到一定程度。英伟达首席执行官黄仁勋甚至表示,除了台积电之外,NVIDIA 别无选择,尤其是在 CoWoS 领域。“这是一种非常先进的封装技术,很抱歉,我们目前没有其他选择。”黄仁勋如是说。

这个技术也为台积电带来了很多收入,有消息指出他们甚至超越日月光,成为全球最大封测玩家。不过他们并没止步,公司过去两年也在大幅扩张CoWoS产能。与此同时,一些技术的新变化,也正在悄然产生。

CoWoS的演进瓶颈

关于台积电的CoWoS,在半导体行业观察之前的文章《杀疯了的CoWoS》中,我们有了很深入的描述。但在这里我们要注意一个点,那就是英伟达在最新的Blackwell 系列产品中将使用更多的CoWoS-L 封装产能,减少 CoWoS-S 封装产能。

据路透社报道,黄仁勋在日月光科技子公司硅品精密工业有限公司(SPIL)举行的先进封装工厂正式启用新闻发布会上表示:“随着我们进入Blackwell,我们将主要使用 CoWoS-L 封装。” “当然,我们仍在生产 Hopper 封装,Hopper 封装也将使用 CowoS-S 封装。我们还将把 CoWoS-S 封装的产能转换为 CoWoS-L 封装。因此,我们并非要减少产能,而是要增加 CoWoS-L 封装的产能。”

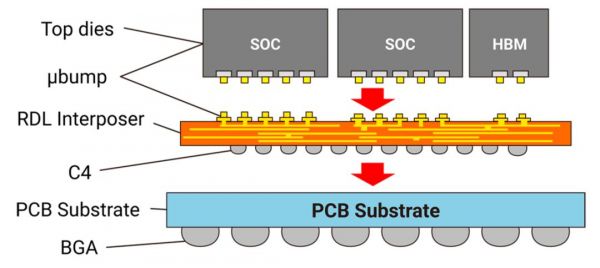

之所以做出这个决定,背后一个重要原因是基于 Blackwell 架构的 NvidiaB100和B200 GPU 需要两个计算芯片,并且需要以 10 TB/s 的带宽进行互连。而台积电的 CoWoS-L 技术实现了这一点,该技术使用局部硅互连 (LSI) 桥接器和充当重分布层 (RDL) 的有机中介层。

台积电CoWoS-L

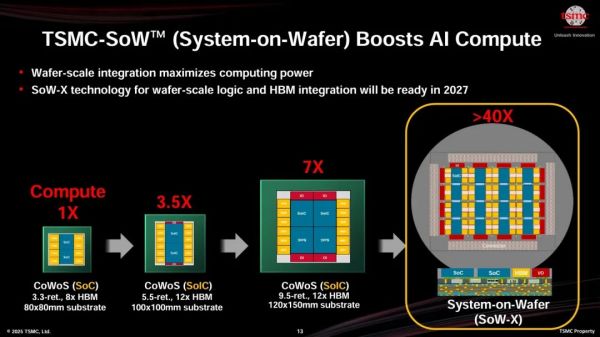

但是,我们也必须意识到,随着芯片尺寸不断增大的趋势,例如 AI 芯片尺寸可能达到 80x84 毫米,一块 12 英寸晶圆只能容纳四个这样的芯片。此外,超大尺寸CoWoS封装面临着与基板尺寸和散热相关的挑战。例如,5.5倍光罩版本需要100x100毫米的基板,而9倍光罩版本则超过120x120毫米。大尺寸基板将影响系统设计和数据中心配置,尤其是在电源和冷却系统方面。在功耗方面,高性能处理器每机架功耗可能达到数百千瓦,这使得液冷和浸入式冷却技术能够更有效地管理散热。

与此同时,台积电过去一直在CoWoS中使用助焊剂。助焊剂的作用是提高连接芯片和中介层的微型凸块的附着力,并防止形成降低键合质量的氧化膜。然而,CoWoS 正逐渐演变成一种越来越难以使用助焊剂的环境。凸块键合后必须清除(清洁)助焊剂,但随着中介层尺寸的增大,很难完全清除积聚在中心的助焊剂。如果助焊剂残留,可能会影响芯片的可靠性。

事实上,台积电也正在聚焦解决这些问题。

例如针对助焊剂的问题,据报道,台积电正在积极探讨无助焊剂键合技术在CoWoS上的应用。报道指出,在去年在提升CoWoS良率方面遇到了困难之后,台积电不得不将重点放在包括无助焊剂键合在内的替代技术上。

半导体业内人士此前透露,“台积电目前正在少量进口无助焊剂键合机,并在研发阶段进行评估”,“我们预计今年年底完成测试”。

来到中介层尺寸尺寸方面,截至 2023 年,台积电 CoWoS 封装中的中介层尺寸为 80x80mm。它大约比光罩大 3.3 倍。按照台积电计划,到2026年,将推出具有 5.5 倍掩模尺寸的 CoWoS-L 。具有创纪录的 9.5 倍掩模尺寸、集成 12+ HBM 堆栈的 CoWoS 也有望于 2027 年推出。在台积电的路线图中,还有一个叫做SoW-X (System-on-Wafer)的技术,与 CoWoS 相比,其性能提高了 40 倍,模拟了完整的服务器机架功能,计划于 2027 年实现量产。

但是,这并没有舒缓大家的担忧,这也正是FOPLP(Fan-out panel-level packaging)最近半年累累被提及的原因之一。在此前文章《FOPLP来袭,CoWoS压力大增》中,我们也对此进行了介绍。相关报道也指出,台积电在这个技术上也有布局。

然而近日,另一则消息透露,台积电将押注CoPoS技术,并计划于于 2029 年实现量产。而英伟达,则有望成为他们的第一个客户。

颠覆传统中介层

CoPoS是Chip-on-Panel-on-Substrate的缩写,作为对比,CoWoS是Chip-on-Wafer-on-Substrate。从这个命名全程可以看到,就是中间的这个wafer换成了panel。

从技术上看,CoPoS 本质上是将中介层“面板化”,创建所谓的面板 RDL(重分布层),或者将芯片放置在“面板级 RDL 层”上。这让即使是 510x515 毫米的面板,也能容纳数倍于 300 毫米晶圆的芯片数量。

来到台积电方面,CoPoS本质上就是CoWoS-L和CoWoS-R的方形面板演进,将传统的圆形晶圆替换为矩形基板。据报道,矩形设计尺寸为310x310毫米,比传统的圆形晶圆提供了更大的可用基板空间,从而提高了产出效率并降低了成本。

据台媒透露,台积电位于嘉义的 AP7 工厂正逐渐成为下一代先进封装的关键枢纽。该工厂计划分八个阶段建设,并将在第四阶段开始大规模生产 CoPoS。台媒进一步报道,AP7 的第一阶段(P1)将作为苹果的专用 WMCM(多芯片模块)基地,而第二阶段和第三阶段则专注于提升 SoIC 的产量。值得注意的是,该报道称,AP7 并未计划生产 CoWoS,而是将保留在 AP8,该工厂由群创光电的旧工厂改建而成。

聪明的你一定发现,无论是FOPLP还是COPOS,都是与面板有关,那这两者又有啥区别呢?

首先,如上所述,FOPLP(扇出型面板级封装)和 CoPoS(基板上面板芯片封装)均采用大型面板基板进行封装。但是,他们在架构和应用方面存在显著差异,尤其是在中介层(interposer)的使用方面。FOPLP 是一种无需中介层的封装方法,芯片直接重新分布在面板基板上,并通过重分布层 (RDL) 进行互连。这种方法具有成本低、I/O 密度高、外形尺寸灵活等优势,适用于边缘 AI、移动设备和集成密度适中的中端 ASIC 等应用。

相比之下,CoPoS 采用了中介层,从而实现了更高的信号完整性和稳定的功率传输——这在集成多个高性能、高功率芯片(例如 GPU 和 HBM)时尤为重要。中介层的存在使 CoPoS 更适合需要大面积封装和高速数据传输的高端 AI 和 HPC 系统。

此外,据了解。CoPoS 中的中介层材料正在从传统的硅演变为玻璃,从而提供更高的成本效益和热稳定性。

资料显示,与传统有机基板相比,玻璃芯基板具有更高的互连密度、更灵活的信号布线、更少的 RDL 层数、更高的带宽密度以及更低的单次数据传输功耗。尤其值得一提的是,采用 TGV(玻璃通孔)技术,损耗极小,且材料的平整度、CTE(热膨胀系数)、刚性、吸湿性和导热性等性能都相对理想。此外,它还具有优异的机械和电气特性,以及光传输应用的潜力。

这也是台积电将 CoPoS 定位为未来 CoWoS-L 的潜在替代品的原因之一。据了解,未来CoPoS封装市场锁定AI等高级应用,其中采用CoWoS-R制程的将锁定博通,CoWoS-L则是目标服务英伟达及超微。

业界分析,CoPoS舍弃传统的圆形晶圆,化圆为方,直接将芯片排列于大型方形面板基板上,大幅提升产能与面积利用率,CoPoS封装结构更具弹性,适合多样化芯片尺寸与应用需求,在AI、5G与高效能运算领域展现强大竞争力。

写在最后

虽然好处不少,但我们要明白,如果一个看起来很好的技术如果还没有被普及,那就肯定是因为它还有一些还没有被客户的短板。

例如这个从圆形封装工艺到方形封装工艺的转变,就需要投入大量的材料和设备研发。而为了实现高精细的导体图案,还需克服翘曲、均匀度等问题,因为这对良率将是一个挑战。另外,客户对RDL 线宽/间距的要求从10µm 缩小到 5µm,甚至 2µm、1µm,这就需要供应商在RDL 布局方面实现新的突破。

总而言之,未来可期,仍需努力。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:穆梓,36氪经授权发布。

相关推荐

台积电,颠覆封装?

先进封装,台积电的另一把尖刀

台积电CoWoS先进封装产能告急!

台积电斥资 900 亿元新台币建设先进封装厂

台积电发力面板级先进封装技术

台积电 vs 英特尔 vs 三星:决战半导体3D封装

台积电CoWoS产能将提升4倍,台企抱团发展先进封装生态

台积电宣布新建先进封装晶圆厂,投资额或达900亿新台币

用台积电的方式打败台积电

台积电新厂或将延迟量产:封装仍在中国完成

网址: 台积电,颠覆封装? http://m.xishuta.com/newsview137274.html