台积电 vs 英特尔 vs 三星:决战半导体3D封装

本文来自微信公众号:芯东西(ID:aichip001),作者:心缘,题图来自:视觉中国

芯东西9月8日报道,近日,中国台湾工业技术研究院研究总监Yang Rui预测,台积电将在芯片制造业再占主导地位五年,此后3D封装将成为主要工艺挑战。

过去十年各种计算工作负载飞速发展,而摩尔定律却屡屡被传将走到尽头。面对更家多样化的计算应用需求,为了将更多功能“塞”到同一颗芯片里,先进封装技术成为持续优化芯片性能和成本的关键创新路径。

台积电、英特尔、三星均在加速3D封装技术的部署。今年8月,这三大芯片制造巨头均亮出,使得这一战场愈发硝烟四起。

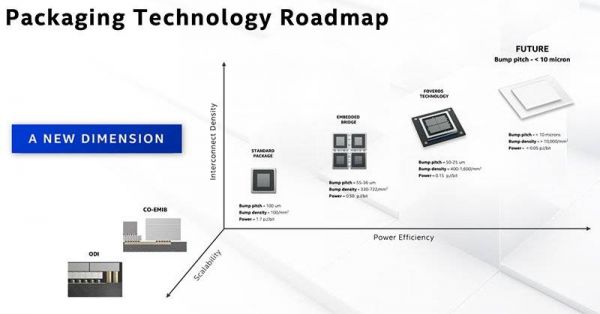

▲英特尔封装技术路线图

通过三大芯片制造巨头的先进封装布局,我们可以看到在接下来的一年,3D封装技术将是超越摩尔定律的重要杀手锏。

一、先进封装:将更多功能塞进一颗芯片

此前芯片多采用2D平面封装技术,但随着异构计算应用需求的增加,能将不同尺寸、不同制程工艺、不同材料的芯片集成整合的3D封装技术,已成为兼顾更高性能和更高灵活性的必要选择。

从最新3D封装技术落地进展来看,英特尔Lakefield采用3D封装技术Foveros,台积电的3D封装技术SoIC按原计划将在2021年量产,三星的3D封装技术已应用于7nm EUV芯片。

为什么要迈向先进封装技术?主要原因有二点,一是迄今处理器的大多数性能限制来自内存带宽,二是生产率提高。

一方面,存储带宽的开发速度远远低于处理器逻辑电路的速度,因此存在“内存墙”的问题。

在传统PCB封装中,走线密度和信号传输速率难以提升,因而内存带宽缓慢增长。而先进封装的走线密度短,信号传输速率有很大的提升空间,同时能大大提高互连密度,因而先进封装技术成为解决内存墙问题的主要方法之一。

另一方面,高性能处理器的体系架构越来越复杂,晶体管的数量也在增加,但先进的半导体工艺仍然很昂贵,并且生产率也不令人满意。

在半导体制造中,芯片面积越小,往往成品率越高。为了降低使用先进半导体技术的成本并提高良率,一种有效的方法是将大芯片切分成多个小芯片,然后使用先进的封装技术将它们连接在一起。

在这一背景下,以台积电、英特尔、三星为代表的三大芯片巨头正积极探索3D封装技术及其他先进封装技术。

二、台积电的3D封装组合拳

今年8月底,台积电推出3DFabric整合技术平台,旨在加快系统级方案的创新速度,并缩短上市时间。

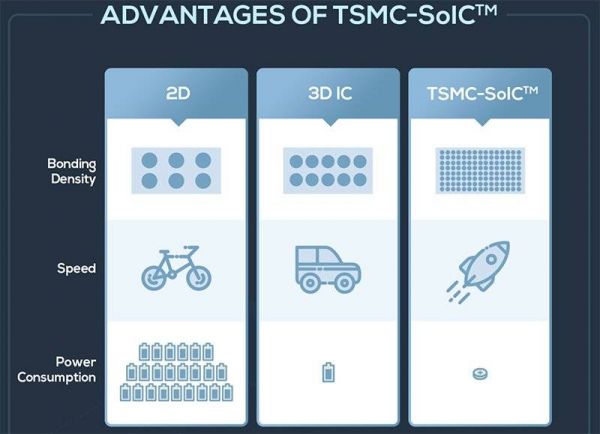

台积电3DFabric可将各种逻辑、存储器件或专用芯片与SoC集成在一起,为高性能计算机、智能手机、IoT边缘设备等应用提供更小尺寸的芯片,并且可通过将高密度互连芯片集成到封装模块中,从而提高带宽、延迟和电源效率。

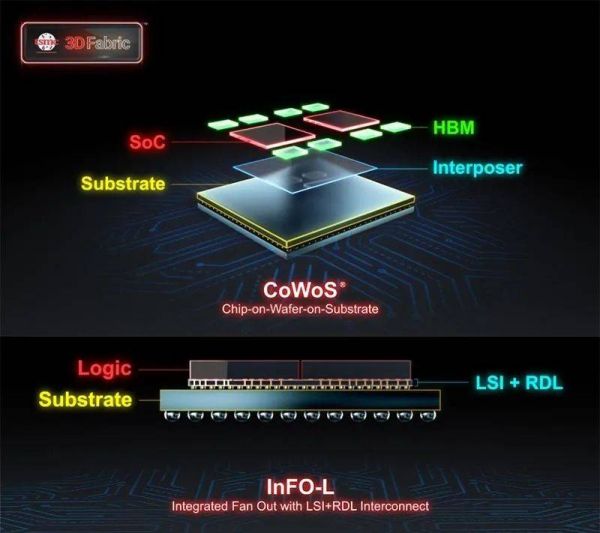

3DFabric由台积电前端和后端封装技术组成。

前端3D IC技术为台积电SoIC技术,于2018年首次对外公布,支持CoW(Chip on Wafer)和WoW(Wafer on Wafer)两种键合方式。

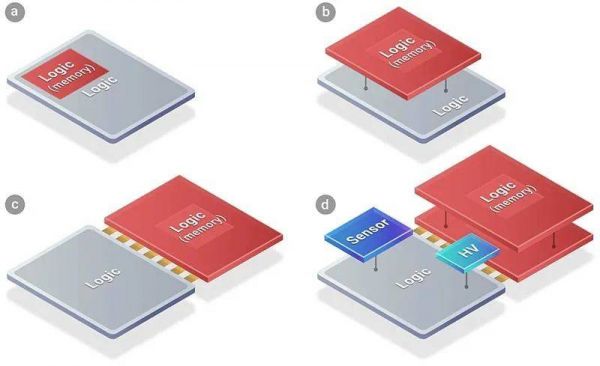

▲a为芯片分割前的SoC;b、c、d为台积电SoIC服务平台支持的多种分区小芯片和重新集成方案

通过采用硅穿孔(TSV)技术,台积电SoIC技术可达到无凸起的键合结构, 从而可将不同尺寸、制程、材料的小芯片重新集成到一个类似SoC的集成芯片中,使最终的集成芯片面积更小,并且系统性能优于原来的SoC。

台积电后端技术包括CoWoS(Chip on Wafer on Substrate)和InFO(Integrated Fan-out)系列封装技术,已经广泛落地。例如今年全球TOP 500超算榜排名第一的日本超算“富岳”所搭载的Fujitsu A64FX 处理器采用了台积电CoWoS封装技术,苹果手机芯片采用了台积电InFO封装技术。

此外,台积电拥有多个专门的后端晶圆厂,负责组装和测试包括3D堆叠芯片在内的硅芯片,将其加工成封装后的设备。

这带来的一大好处是,客户可以在模拟IO、射频等不经常更改、扩展性不大的模块上采用更成熟、更低成本的半导体技术,在核心逻辑设计上采用最先进的半导体技术,既节约了成本,又缩短了新产品的上市时间。

台积电3DFabric将先进的逻辑、高速存储器件集成到封装模块中。在给定的带宽下,高带宽内存(HBM)较宽的接口使其能以较低的时钟速度运行,从而减少功耗。

如果以数据中心规模来看,这些逻辑和HBM器件节省的成本十分可观。

三、英特尔用“分解设计”策略打出差异化优势

和台积电相似,英特尔也早已在封装领域布局了多种维度的先进封装技术。

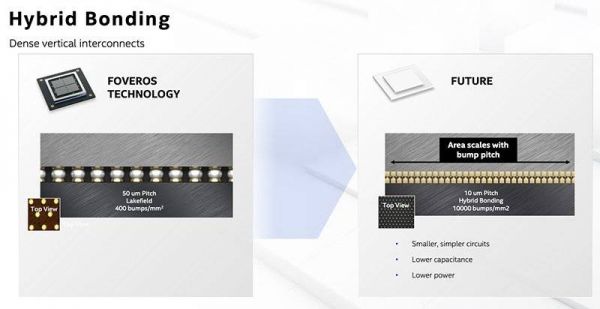

在8月13日的2020年英特尔架构日上,英特尔发布一个全新的混合结合(Integrated Fan-out)技术,使用这一技术的测试芯片已在2020年第二季度流片。

相比当前大多数封装技术所使用的热压结合(Thermocompression bonding)技术,混合结合技术可将凸点间距降到10微米以下,提供更高互连密度、更高带宽和更低功率。

▲英特尔混合结合技术

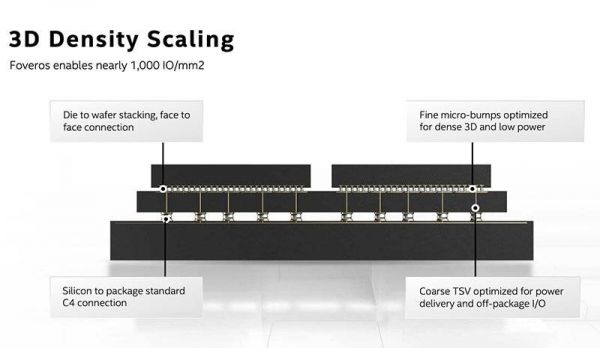

此前英特尔已推出标准封装、2.5D嵌入式多互连桥(EMIB)技术、3D封装Foveros技术、将EMIB与Foveros相结合的Co-EMIB技术、全方位互连(ODI)技术和多模I/O(MDIO)技术等,这些封装互连技术相互叠加后,能带来更大的可扩展性和灵活性。

据英特尔研究院院长宋继强介绍:“封装技术的发展就像我们盖房子,一开始盖的是茅庐单间,然后盖成四合院,最后到高楼大厦。以Foveros 3D来说,它所实现的就是在建高楼的时候,能够让线路以低功率同时高速率地进行传输。”

他认为,英特尔在封装技术的优势在于,可以更早地知道未来这个房子会怎么搭,也就是说可以更好地对未来芯片进行设计。

面向未来的异构计算趋势,英特尔推出“分解设计(Digression design)”策略,结合新的设计方法和先进的封装技术,将关键的架构组件拆分为仍在统一封装中单独晶片。

也就是说,将原先整个SoC芯片“化整为零”,先做成如CPU、GPU、I/O等几个大部分,再将SoC的细粒度进一步提升,将以前按照功能性来组合的思路,转变为按晶片IP来进行组合。

这种思路的好处是,不仅能提升芯片设计效率、减少产品化的时间,而且能有效减少此前复杂设计所带来的Bug数量。

“原来一定要放到一个晶片上做的方案,现在可以转换成多晶片来做。另外,不仅可以利用英特尔的多节点制程工艺,也可以利用合作伙伴的工艺。”宋继强解释。

这些分解开的小部件整合起来之后,速度快、带宽足,同时还能实现低功耗,有很大的灵活性,将成为英特尔的一大差异性优势。

四、三星首秀3D封装技术,可用于7nm工艺

除了台积电和英特尔外,三星也在加速其3D封装技术的部署。

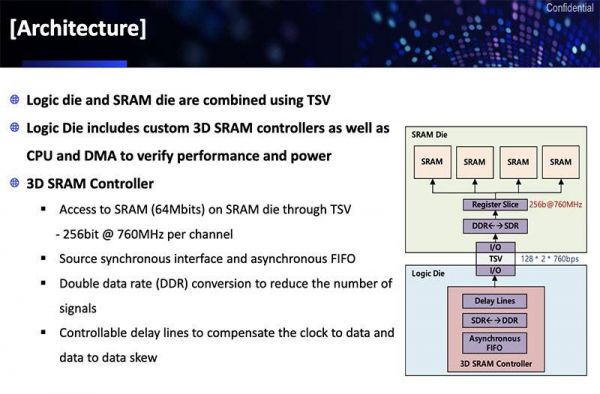

8月13日,三星也公布了其3D封装技术为“eXtended-Cube”,简称“X-Cube”,通过TSV进行互连,已能用于7nm乃至5nm工艺。

据三星介绍,目前其X-Cube测试芯片可以做到将SRAM层堆叠在逻辑层上,可将SRAM与逻辑部分分离,从而能腾出更多空间来堆栈更多内存。

▲三星X-Cube测试芯片架构

此外,TSV技术能大幅缩短裸片间的信号距离,提高数据传输速度和降低功耗。

三星称,该3D封装技术在速度和功效方面实现了重大飞跃,将帮助满足5G、AI、AR、VR、HPC、移动和可穿戴设备等前沿应用领域的严格性能要求。

五、结语:三大芯片巨头强攻先进封装

可以看到,在2020年,围绕3D封装技术的战火继续升级,台积电、英特尔、三星这三大先进芯片制造商纷纷加码,探索更广阔的芯片创新空间。

尽管这些技术方法的核心细节有所不同,但殊途同归,都是为了持续提升芯片密度、实现更为复杂和灵活的系统级芯片,以满足客户日益丰富的应用需求。

而随着制程工艺逼近极限,以及应用需求的持续多元化,未来芯片制造商除了要解决散热等技术挑战外,还有望推进来自不同厂商的先进封装技术的融合。

本文来自微信公众号:芯东西(ID:aichip001),作者:心缘

相关推荐

台积电 vs 英特尔 vs 三星:决战半导体3D封装

芯片制程之战:三星台积电挺进3nm,英特尔们呢?

台积电攻防战

台积电登顶的三个节点

英特尔退位,台积电称王

全球芯片业大变局:台积电的野望和英特尔溃败

台积电收到6nm订单,“牙膏厂”要靠外援撑过下半场?

台积电、英特尔、三星投资ASML的真相

成为台积电

半导体教父回归A股,欲再造一家“台积电”?

网址: 台积电 vs 英特尔 vs 三星:决战半导体3D封装 http://m.xishuta.com/newsview30611.html