巨头混战制程争霸赛,芯片真的越小越好吗?

编者按:本文来自腾讯科技,36氪经授权发布。

先是老牌芯片制造商IBM宣布研发出2nm芯片,紧接着台积电宣布重大成果:发现二维材料结合半金属铋(Bi)能达到极低的电阻,接近量子极限,可以满足1nm制程的需求。

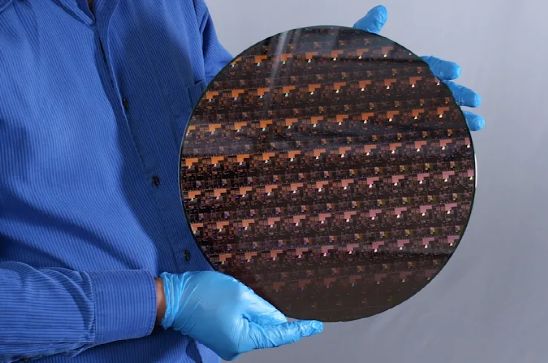

IBM的2纳米晶圆

为何芯片巨头们都在追求更小制程的芯片?芯片真的越小越好吗?更小制程的芯片除了提升手机性能外,对于我们普通人来说还有哪些应用场景?

云岫资本合伙人兼首席技术官赵占祥认为,巨头追求更小工艺制程的原因有很多,“第一,可大幅提高晶体管的密度;第二,会带来性能的大幅提升——以CPU为例,一个工艺的演进就是50%的性能进步,Intel在制程上的落后在一段时间内限制了他的性能提升;第三,可以带来更低的功耗,这在移动设备和数据中心中的需求更高,对数据中心而言,每TOPS/W的功耗优化,可以带来近百美金的用电、运维成本降低。 ”

另外,需求驱动。“目前主要驱动力是在手机CPU、平板电脑CPU、个人电脑或服务器CPU、GPU芯片、各种AI芯片,还有FPGA芯片,包括一部分虚拟货币矿机芯片等,主要是追求更高的数据处理能力,或者说是芯片更高集成度的应用场景上。”中科创星董事总经理卢小保认为。

但芯片制程并不能无限小下去。

AMD高级数字芯片设计工程师温戈表示,目前的3nm已基本接近工艺极限。“在制程达到7nm以下之后,短沟道效应和量子遂穿效应会越来越明显,这将对工艺带来极大的挑战。另外硅原子的直径在0.117nm左右,1nm的沟道长度也就不到9个原子的宽度,从物理层面来讲,这是很难实现的。”

另外,“随着栅极尺寸的缩小,栅极控制电流的能力下降,漏电加剧从而会导致芯片失效。”南京大学物理学博士乔通补充。

而更小制程的芯片,“未来AI和自动驾驶等场景可能会受益。但在手机端,可以说并未出现新的应用场景,甚至当前的处理器性能对手机来说,已经是过剩的”。温戈认为。

在本期《你问我答》中,我们邀请业内人士和大家一起讨论。以下是精华内容摘录:

追求更小制程,可以提升性能,降低功耗

@赵占祥 云岫资本合伙人兼CTO

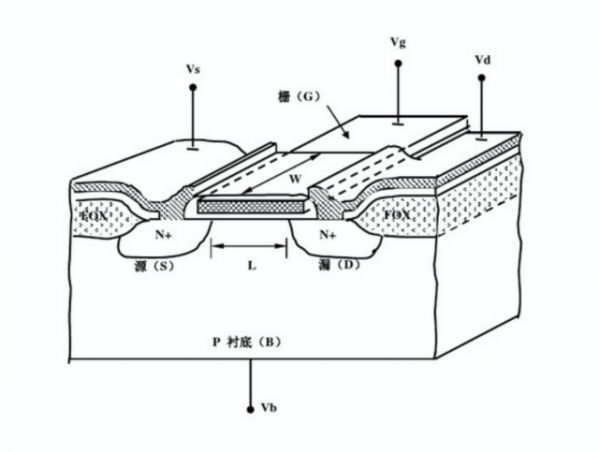

芯片制程一般意义上是栅极的最小线宽,而栅极的宽度决定了电流通过时的损耗,表现出来就是手机常见的发热和功耗,宽度越窄,功耗越低。但是目前随着先进制程的发展,5nm、3nm已经不再代表栅极的最小线宽,而是等效长度。

图片源于网络

巨头追求更小工艺制程的原因有很多:第一,可大幅提高晶体管的密度;第二,会带来性能的大幅提升——以CPU为例,一个工艺的演进就是50%的性能进步,Intel在制程上的落后在一段时间内限制了他的性能提升;第三,可以带来更低的功耗,这在移动设备和数据中心中的需求更高,对数据中心而言,每TOPS/W的功耗优化,可以带来近百美金的用电、运维成本降低。

图片源于网络

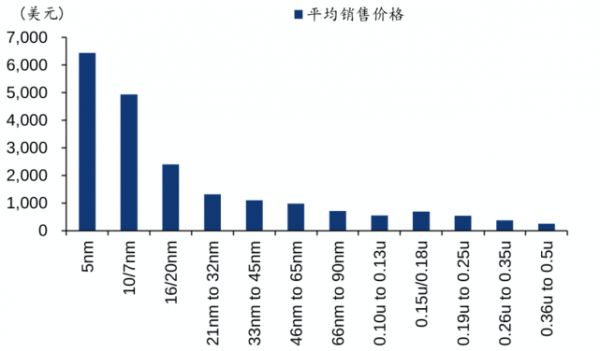

但是另一方面,随着工艺制程不断逼近物理极限,单从芯片自身成本来看,曾经工艺制程进步带来的成本大幅度优化已经不显著了,目前主要是材料和结构、设备等需求导致了制造成本的飙升。

@卢小保 中科创星董事总经理

目前在持续推进半导体先进工艺的主要是一些国际巨头,如TSMC、Intel、Samsung等。

半导体制造工艺的迭代主要是由摩尔定理驱动发展的,即:集成电路上可以容纳的晶体管数目在大约每经过18个月便会增加一倍。摩尔定理的存在,意味着同样的性能的芯片产品,每18个月价格就会下降50%,或者说同样价格的集成电路产品每18个月性能就会提升100%。

摩尔定理是由产业巨头主导的产业发展规划,驱动和促使整个产业上下游链条各环节所有企业按照同样的节奏去发展协同,每个环节既不要太快、也不要太慢。某种程度上,摩尔定理协调了整个集成电路产业的发展节奏,可以说是半导体产业的“五十年规划”。

但集成电路产业经过五十多年的发展,摩尔定理已经式微,虽然先进工艺仍在几乎沿着摩尔定理的规划持续进步,但其技术复杂度越来越难,实现成本也越来越高,能够承担高昂研发和制造成本的芯片产品越来越少。

目前主要是对性能提升非常敏感的手机CPU、平板CPU、个人电脑CPU、GPU等,或者是对算力需求持续提升的场景如各种AI芯片、矿机芯片等,在这些场景里面,先进工艺带来的芯片性能提升仍然足以抵消芯片研发成本的大幅增加。

但是越来越多的应用场景、越来越多的芯片种类,在达到性能的阈值点后,持续提升集成度已经意义不大。采用先进工艺,一次性研发和生产投入负担太重,反而采用成熟工艺如28nm、40nm、55nm等,甚至是8寸工艺,性价比会更高,比如TWS耳机芯片、手表芯片,各种车载芯片、各种家电芯片,物联网芯片等。

另外,由于先进工艺研发和制造成本的快速增加,通过芯片制造提升芯片性能/集成度的代价上升太快,投入产出比越来越小,但需求端仍有持续提升性能/集成度的要求。

在这个矛盾下,也迫使产业界另辟蹊径,开始思考通过其它的技术方式,如封装技术提升芯片性能/集成度,chiplet技术也因此开始快速推进应用。通过chiplet技术,使用10nm工艺制造出来的芯片,完全也可以达到7nm芯片的集成度,但是研发投入和一次性生产投入则比7nm芯片的投入要少的多。

3nm芯片,已经接近工艺极限

@温戈 AMD高级数字芯片设计工程师

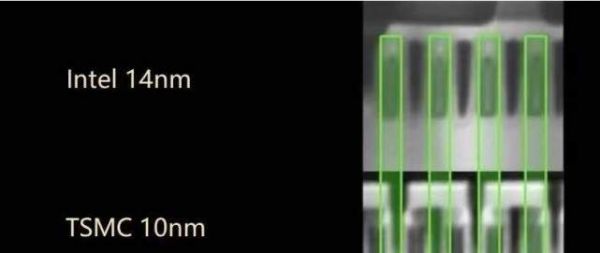

要说芯片制程命名,那肯定是台积电玩的最溜。

上图就是英特尔14nm和台积电10nm的晶体管栅格宽度对比,事实上并没有差太多。

5nm、3nm工艺中的nm,指的是晶体管导电沟道的长度,通常也认为是晶体管的栅极宽度。

在整个芯片电路中,晶体管的栅极是最窄的线条。如果栅极宽度为3nm,则将其称为3nm工艺制程。

目前的3nm工艺下,基本已经接进工艺极限。在FinFET晶体管时代,即22nm以下,工艺制程已经不是真正的沟道长度,而是根据晶体管密度和芯片面积算出的等效工艺制程。

就硅基芯片来看,制程是没办法一直小下去的,在制程达到7nm以下之后,短沟道效应和量子遂穿效应会越来越明显,这将对工艺带来极大的挑战。另外硅原子的直径在0.117nm左右,1nm的沟道长度也就不到9个原子的宽度,从物理层面来讲,这是很难实现的。

在5nm及以下,制程更小的芯片投入产出比越来越低,非常不合理。如果不是寡头通吃,那么台积电一定是亏损的。

@乔通 南京大学物理学博士

随着半导体工艺技术的进步,芯片的尺寸越来越小,已经进入10nm以下时代。

原本芯片的纳米数指的是晶体管栅极的长度,代表芯片制造工艺的水平,但目前最先进的5nm、3nm只是工艺代号,已经不再是栅极的物理长度了。

因为随着栅极尺寸的缩小,栅极控制电流的能力下降,漏电加剧从而导致芯片失效。除此之外,尺寸缩小到一定程度更是会出现量子效应,这也是制约芯片无限制缩小下去的原因。

但是采用了更先进制程工艺的芯片性能更强、功耗更低,所以科技巨头比如华为、苹果等都在孜孜不倦地追求更小尺寸的芯片。

目前芯片的缩小化存在两大难题:一是制造工艺愈发复杂化,二是成本越来越高。芯片尺寸的缩小导致工艺步骤大大增加,成本也持续上升,所以负担得起的公司也越来越少。

随着5G、AI、智能电动汽车等产业的蓬勃发展,产业界对先进制程工艺芯片的需求也在持续提高,预计未来越来越多的公司会平衡芯片尺寸与芯片成本,选择适合自己的工艺。

未来应用场景:AI、挖矿、自动驾驶

@卢小保 中科创星董事总经理

先进制程如7nm、5nm工艺目前主要应用的驱动力是在手机CPU、平板电脑CPU、个人电脑或服务器CPU、GPU芯片、各种AI芯片,还有FPGA芯片,包括一部分虚拟货币矿机芯片等,主要是追求更高的数据处理能力,或者说是芯片更高集成度的应用场景上。

其中典型的消费类应用主要是手机、平板电脑、PC等。

其它消费类应用如TWS耳机、手表、手环等数码产品的CPU芯片,基本上以28nm、22nm为主流工艺平台进行生产,相关产品应用到的其它芯片如通信、存储、传感器、电源等,则以28nm、40nm、65nm等各种成熟工艺,甚至传感器、电源应用的都是8寸工艺。

@温戈 AMD高级数字芯片设计工程师

以目前的情况来看,制程的提升会带来更高的性能,未来AI和自动驾驶等场景可能会受益。在手机端,可以说并出现新的应用场景,甚至当前的处理器性能对手机来说已经是过剩的。

相关推荐

巨头混战制程争霸赛,芯片真的越小越好吗?

旗舰手机的充电器,原来体积越小越高端?

低温奶上演“时间战” 时间越短真的越好吗?

咖啡馆越开越小,3㎡就能实现梦想?

手机厂家与芯片企业的焦虑,5G前夜的混战已经打响

芯片制程:28nm向3nm的“大跃进”

芯片制程之战:三星台积电挺进3nm,英特尔们呢?

晶圆代工扩产,越烧越热

深思美国反垄断风暴:拆分巨头真的好吗?

AI芯片混战:云端和终端均有长足发展

网址: 巨头混战制程争霸赛,芯片真的越小越好吗? http://m.xishuta.com/newsview44236.html