实现2nm工艺突破,台积电为何能给“摩尔定律”续命?

本文作者:海怪,题图来自:视觉中国

今年,因为美国对华为、中芯国际的禁令的关系,台积电这家原本处在芯片产业的后端的芯片制造企业,被一次又一次地搬到聚光灯前,接受外界对其里里外外的检视。

恰好此时,台积电正在迎来其发展的高光时刻。虽然在9月份华为禁令生效之后,台积电失去了华为的大额订单,但是空出来的产能立刻被苹果、高通等公司瓜分,并处在满载生产状态。叠加疫情下电子消费产品增长等因素,台积电将在今年迎来超过全球晶圆代工厂的产业成长率高出10%的增长。

特别是台积电领先其他晶圆代工厂的5nm7nm制程的营收占比超过43%,营收能力堪比“印钞机”。与此同时,台积电在更先进制程的研发和设备投入上更加不遗余力。

为应对新制程工艺产能扩大的需求,台积电已经向ASML订购了新的13台极紫外(EUV)光刻机,要求在2021年全部交付。据估算,13套EUV可能使台积电花费高达22.84亿美元。同时,台积电刚刚决定明年起大幅涨薪达20%,一方面为激励员工,一方面为招揽人才、避免被其他对手高薪挖人,用真金白银来留住那些愿意继续为造芯“爆肝”的工程师们。

在一片繁荣的商业前景之下,台积电在更先进制程的技术布局上面也保持着领先。据台湾媒体报道,近日台积电在2nm工艺制程上取得了重大突破,研发进度超越预期,有望在2023年下半年,风险试产的良率可以达到90%。

相比较于关注热闹的当下,我们不妨追踪这条技术线索,来看下台积电保持先进制程工艺的经验,看下它是如何来为游走在失效边缘的摩尔定律来“续命”的。

2nm已突破,1nm也没问题

我们先从技术层面来看下台积电这次制程工艺的突破。

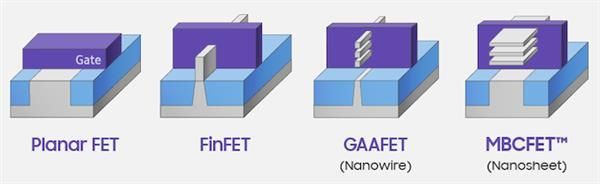

台积电在2nm制程工艺上的突破,来自于采用了全新的GAA晶体管架构。区别于3nm和5nm制程所采用的鳍式场效晶体管(FinFET)架构,这次2nm改用了全新的多桥通道场效晶体管(MBCFET)架构,这一架构是以环绕闸极(GAA)制程为基础的架构,可以解决FinFETch因为制程微缩而产生的电流控制漏电等物理极限问题。

可以说,GAA制程工艺的出现,相当于又给摩尔定律续命了五年左右。摩尔定律说的是,每18到24个月,集成电路上可容纳的元器件数目便会增加一倍,芯片的性能也会随之翻一番。

我们知道,这个定律并非一定会发生的定理,而只是一个预测,这个预测是建立在半导体制程工艺能够稳步提升的情况下,但现在半导体产业依赖FinFET架构,已经实现了7nm和5nm制程的芯片量产,很多人买到的最新的iPhone12、华为Mate40就采用的是5nm制程的芯片。

不过,随着晶体管尺度向5nm甚至3nm迈进,FinFET本身的尺寸已经缩小至极限后,无论是鳍片距离、短沟道效应、还是漏电和材料极限也使得晶体管制造变得难以完成。

现在,依托FinFET技术,台积电的芯片工艺制程的终点来到了3nm,再向下就遇到瓶颈。根据报道,GAA技术是2006年由科学技术研究院和国家纳米晶圆中心开发的一种基于全能门FinFET技术的晶体管,而三星正率先在3nm工艺上采用了基于GAA技术开发的MBCFET架构形态。出于稳健考虑,台积电则选择在第一代3nm工艺将继续用FinFET技术,而2nm工艺上采用了三星一样的MBCFET架构。

台积电在新制程上的进展,将为新一代芯片的速度效能提升30%到40%,功耗则将降低20%~30%,相应的,新制程的研发成本将高达5亿美元,相较于28nm工艺的0.6亿美元的成本,确实是直线上升。

现在,台积电依靠在EUV微显影技术和纳米片堆叠关键技术上的积累,使得2nm制程的开发良率提升进度超出预期。

根据台积电在最近召开的“2020世界半导体大会”的官方说法,芯片制程工艺将继续推进,摩尔定律将在3nm、2nm、1nm上继续适用。根据目前透露的消息,2nm芯片的生产布局,将在台湾新竹进行建设和研发。

多管齐下,为领先制程布下完整技术图谱

从上面的技术介绍来看,台积电的2nm工艺采取的GAA制程架构,尽管并非自己研发,其在3nm制程上,还没有三星激进地采用MBCFET架构,但想要发挥GAA架构优势,就必须要看到台积电在保持工艺领先性和生产良率上的技术优势和积累。

比如,以3nm工艺为例,台积电继续采用FinFET架构晶体管设计,一方面正是由于其研发团队将FinFET的性能提高到了新的高度,与5nm相比,3nm在速度上有10%~15%的提升,功耗有25~30%的降低,而逻辑密度则提高了1.7倍,SRAM密度也将提升20%,另一方面是由于3nm可以在2022年下半年量产,这样能让下单客户实现技术的快速升级,率先推出领先的产品。

从台积电的技术布局上,我们可以找出其在制程工艺上面的成功因素。

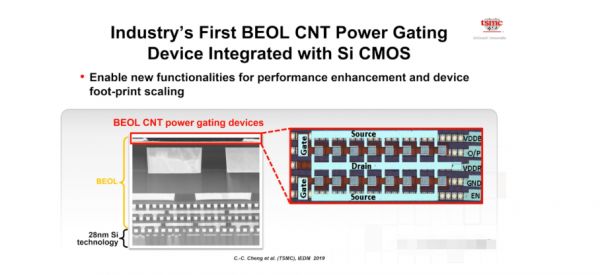

首先是其长期投入获得领先的技术研发优势。比如,为配合新制程工艺的良率,台积电在Nano-Sheet结构上面,已经成功生产出了32 Mb nano-sheet的SRAM,在低电压功耗上面具有明显优势;在2D材料上,台积电基于包括硫化钼和硫化钨在内的的2D硫化材料获得性能非常高的On-current;在电源管理上,台积电的研究人员用碳纳米管嵌入到一个CMOS的设计中,用来替代Power Gating的控制电流作用,给未来的进一步微缩提供新的思路。

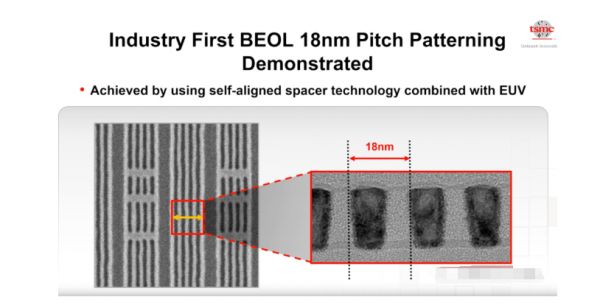

其次是台积电形成的长期的技术合作产业链。ASML作为早期和台积电建立合作的光刻机供应商,在为台积电提供设备的同时,也得到来自台积电的技术反馈。目前,台积电在在EUV光刻技术的OPC、光罩和光阻等多个方面都有投入,比如台积电在EUV技术结合上,采用自对准垫片获得了业内最小的18nm的mental pitch,对晶体管微缩大有帮助。

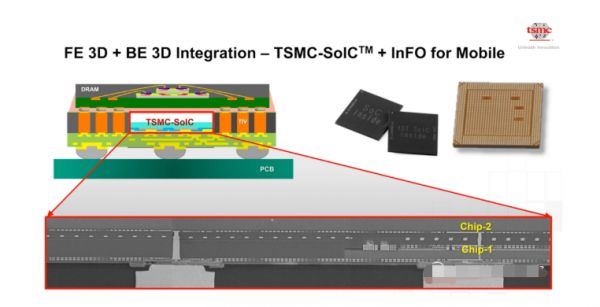

再就是对工艺流程的优化改造。为了应对摩尔定律接近失效的危机,仅仅从微缩晶体管,提高密度以提升芯片性能的角度正在失效。台积电推动了多项前段和后段的3D封装技术,来提升芯片性能。比如在芯片制造前段实现的SOIC 3D堆叠技术,在后段实现的CoWoS和InFo的3D封装技术。这些技术在帮助实现晶体管微缩的同时,进一步提高了良率。

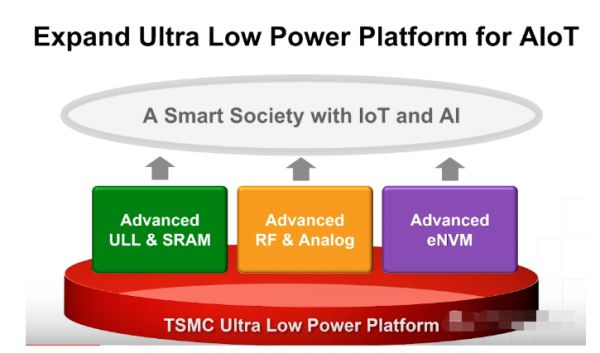

此外,非常重要的一点就是台积电在特殊制程上的长期积累。这可能是很少为人注意的一点。台积电具有MEMS、图像传感器、嵌入式NVM,RF、模拟、高电压和BCD功率IC方面的广泛产线投入。同时,也在逻辑IC技术基础上,加上先进的ULL&SRAM、RF&Analog以及eNVM技术,以实现低功耗以及模拟技术的提升。特殊制程将推出IoT场景和AI场景设备的发展。

以上的一系列技术优势,得益于台积电庞大的研发投入。据数据,近几年,台积电每年的研发投入都达到100亿美元。而台积电在技术路线上的领先布局和长期巨额的研发投入,实际上跟其所创立的Foundry代工厂创新模式有关,也和台积电本身的所处的地缘、产业机遇期有关。

专注投入和自主研发:台积电的技术领先心法

我们看到,台积电在3nm工艺的架构路线稳健推进和领先量产,以及在2nm工艺上的架构路线升级和顺利推进,都源于其在整个半导体晶圆制造上的长期研发投入和技术积累。

而这给了我们一种错觉,似乎完成这些动作就可以实现对半导体产业的主导,能又一次延续摩尔定律的神话。但实际上,这既有台积电创立之初所建立的独特创新模式,也与台积电在几次关键技术路口的正确选择有关。

毕竟,在台积电三十多年的崛起之路上,始终横亘着英特尔这样的IDM整合元器件老前辈以及三星这个强劲的同行老对手,台积电必须在一次次的挑战中走对路、押对注,才能有幸活下来。

台积电能够取得领先工艺制程的根本原因在于,其率先创立的专门专注于芯片制造的代工厂(Foundry)模式。80年代末,台积电创立之初,原本是未来抓住美国“拆解”了日本半导体产业后的产业转移的机会,但如果采用原有设计、制造和封装一体化的DIM模式,将根本无法与欧美厂商竞争,也没有那么雄厚的资金支持。

台积电创始人张忠谋另辟蹊径地拆解出“后端制造”这一个环节,开始了代工厂模式。这一行业垂直化分工带动了一批芯片设计公司的出现,也为台积电的专注制造工艺的发展提供了生存机会。从创立之初,台积电不仅避免了和英特尔的正面竞争,而且还获得了英特尔的第一笔订单和工艺技术的指导。

后面,基于Foundry模式的中立属性,台积电获得了苹果、高通、AMD这些有着竞争关系的客户的长期订单。台积电的模式从而使得整个产业链能够专注发挥自身的优势,而台积电则把全部资源重点投入到先进制程工艺和生产工艺的改进升级上面。

不过,台积电的发展并非一帆风顺,而是在几个关键技术关口的坚持自主研发和正确押注,才使其没有在半导体的淘汰赛中落败。

第一次关键抉择是2003年,台积电拒绝了IBM新开发的铜制程工艺,用自研的技术来打破了IBM的技术钳制。第二次是2004年,台积电准备推动自己研制的“湿法光刻技术”,就在遭到日本尼康、佳能的一致抵制下,与当时还是同处边缘位置的荷兰ASML一拍即合,实现了对光刻技术的颠覆式突破,从此也和ASML结下了革命的友谊。2004年,台积电就拿下了全球一半的芯片代工订单,位列半导体行业规模前十。

第三次是在2009年的全球金融危机之时,台积电深陷三星阻击和业务衰退的双重危机。此时重新回归的张忠谋力挽狂澜,召回已经退休的蒋尚义,开始了扩员、扩研发的大举反击。当时在28纳米制程的关键技术上,台积电选择了后闸级方案,而非三星正在研发的前闸级方案,这一次正确的判断,使得台积电良率大幅提升,三星却仍没有进展。紧接着,台积电用坚定的产线投入和人力打动了苹果。几年后,拿到了苹果A8芯片的全部订单,赢得了发展良机。

而此后,台积电在人才、客户、专利、技术路线上与三星展开激烈交锋,一直持续至今。但台积电在7nm工艺上取得领先之后,其领先优势一直保持至今。而双方的下一个战场,将在3nm工艺上展开。

从这些关键因素和众多的关键环节上,我们可以总结出台积电能够取得先进工艺的技术领先的核心要点:

1. 台积电开创的Foundry模式,使其能够在半导体产业中保持“中立”立场,能够和不同IC设计厂商进行通力合作获得先进的设计方案,又能够心无旁骛地将只专注到晶圆制造的各个工艺环节中,获得了行业垂直分工的专属优势。

2. 台积电在初期确立的自主研发的路线和不遗余力的研发投入,先是摆脱了技术附庸的身份,又在后面一次又一次地摆脱技术专利的围堵,以及实现领先工艺的反超。

3. 除了自身努力的因素,台积电背后身处的美国半导体产业所主导的分工格局,以及苹果、高通等公司为钳制韩国、三星和台湾地区所给予台积电的支持密不可分。订单和市场需求始终是推动先进工艺技术升级的最终驱动力。

台积电的技术领先,从现实竞争上,对我国的半导体产业来说,仍然是一场严峻的挑战。受到美国长臂管辖钳制的台积电,短期内难以在为华为海思这样的先进IC设计企业生产芯片,同时也成为我国的芯片制造代工企业短期内难以企及的竞争对手。

不过,台积电的技术领先的经验,从产业共性上来说,仍然值得国内的厂商学习。在全球半导体产业合作风险充满变数的当下,练好内功,专注核心工艺技术的研发,将是在逆境中前行的不二心法。

相关推荐

实现2nm工艺突破,台积电为何能给“摩尔定律”续命?

台积电迈向2nm,三星和英特尔慌了吗?

最前线丨3nm、5nm制程技术还没捂热,台积电又要开始研发2nm的芯片了

你追我赶的英特尔和台积电

台积电披露3nm工艺更多细节,明年试产

芯片制程之战:三星台积电挺进3nm,英特尔们呢?

成为台积电

华为7亿美元紧急下单台积电?先进制程工艺不容乐观

台积电赴美建厂,华为上海建厂:芯片制造走向何方?

台积电确认断供华为背后:离开华为有人“补位”

网址: 实现2nm工艺突破,台积电为何能给“摩尔定律”续命? http://m.xishuta.com/newsview34531.html