投资100亿美元!美国建High-NA EUV研发中心,意欲何为?

12月13日消息,当地时间11日,美国纽约州长Kathy Hochul宣布,与包括IBM、美光、应用材料(Applied Materials)、东京电子(Tokyo Electron)等半导体大厂达成一项合作协议,预计将投资100亿美元在纽约州Albany NanoTech Complex(奥尔巴尼纳米技术综合体)兴建下一代High-NA EUV半导体研发中心,以支持世界上最复杂、最强大的半导体的研发。

根据声明显示,负责协调该设施建设的非营利性机构NY Creates,预计将利用10亿美元的州政府资金向ASML采购TWINSCAN EXE:5200光刻设备。接下来,一旦设备安装完毕,相关合作伙伴将可以开始研究下一代芯片制造。该计划将创造700个工作岗位,并带来至少90亿美元的民间投资。

这一合作伙伴关系将大大提高纽约州作为确保联邦国家半导体技术中心锚定中心地位的领先候选人的地位,这一指定有可能释放超过110亿美元的《芯片与科学法案》资金。

在人才方面,该计划还包括通过与纽约州立大学的合作,以支持和建设人才发展管道。相关合作伙伴已承诺扩大或启动对劳动力发展计划的支持,包括对纽约州立大学、伦斯勒理工学院以及其他公共和私人劳动力发展活动的投资;K-12 STEM学术项目;工程和相关STEM领域的本科生和研究生的培训、实习和体验式学习,以及学术研究伙伴关系。

NY CREATES和行业合作伙伴还同意在项目的整个建设和运营阶段做出一系列可持续性承诺,这些承诺与纽约州领先的绿色芯片计划密切一致,包括使用最佳可用技术减少温室气体排放;优先考虑可再生能源,优先考虑纽约州的能源;以及为与该项目相关的新建筑争取最低LEED金牌认证。此外,合作伙伴致力于将可持续性作为研发活动的主要目标,包括可持续的半导体制造工艺、材料使用、废物再利用和回收以及晶圆厂设计。通过这一新的重点,High-NA EUV中心将成为可持续和气候友好型半导体制造工艺和技术发展的全球领导者。

为了支持该项目,目前纽约州正在投资10亿美元扩建奥尔巴尼纳米技术综合体,通过购买ASML的EXE:5200 High-NA EUV设备建立High-NA EUV研发中心,高度复杂的建筑,拥有超过50000平方英尺的洁净室空间(未来预计将进一步扩大),这将鼓励未来的合作伙伴增长,并支持新的举措,如美国国家半导体技术中心、国家先进封装制造计划和国防部微电子共享计划,后者最近被授予纽约州。在两年的施工阶段,该项目还将以现行工资创造500至600个工会建筑工作岗位。

纽约州长Kathy Hochul表示:“这项将创新芯片研究带到首都地区的100亿美元合作伙伴关系向整个行业发出一个信息:纽约对商业开放。”。“从我们的绿色芯片立法到美光的历史性投资和GO-SEMI的创建,我们正在纽约建设半导体研究的未来。这个行业通过重大的地区投资、无数的新工作岗位以及对劳动力发展和可持续性的大胆承诺,在我们州创造了真正的机会,我的政府将继续与以及行业领袖,使纽约成为全球芯片制造超级基带。”

ASML总裁兼首席执行官Peter Wennink表示:“我们为ASML工具使我们的客户能够生产世界所需的芯片而感到骄傲。纽约州对尖端High-NA EUV技术的这项重大投资将推动我们生态系统的创新,并加速芯片制造商更快、更具成本效益地制造未来更先进芯片的能力。”

单价超3亿美元,High-NA EUV光刻机成尖端制程升级的关键

由于EUV光刻系统中使用的极紫外光波长(13nm)相比DUV 浸入式光刻系统(193 nm)有着显着降低,多图案 DUV 步骤可以用单次曝光 EUV 步骤代替。可以帮助芯片制造商继续向7nm及以下更先进制程工艺推进的同时,进一步提升效率和降低曝光成本。

自2017年ASML的第一台量产的EUV光刻机正式推出以来,三星的7nm、5nm、3nm工艺,台积电的第二代7nm、5nm、3nm工艺的量产都是依赖于0.33 数值孔径的EUV光刻机来进行生产。

目前,随着三星、台积电、英特尔3nm制程的相继量产,目前这三大先进制程制造厂商都在积极投资2nm制程的研发,以满足未来高性能计算等先进芯片需求,并在晶圆代工市场的竞争当中取得优势。而2nm工艺的实现则可能需要依赖于ASML新一代的高数值孔径 (High-NA) EUV光刻机EXE:5000系列。

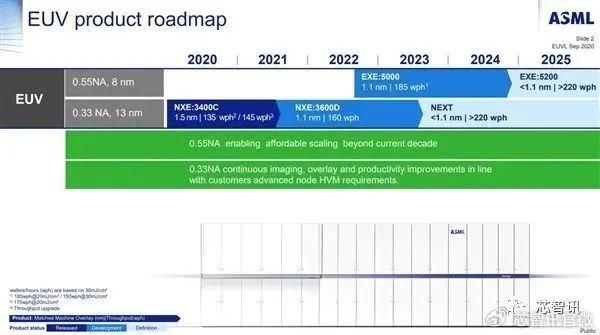

ASML开发的第一代EUV光刻机是基于 0.33 数值孔径透镜的 EUV 光刻系统。比如目前被众多晶圆制造商采用的ASML Twinscan NXE:3400C和NXE:3400D,都是基于0.33 NA镜头,分辨率为13nm。这样的分辨率适合在金属间距介于30nm和38nm之间的制造技术上使用。但是,当金属间距来到30nm以下,也就是制程节点达到5nm之际,13nm的分辨率就不够用了,这使得芯片制造商将不得不使用EUV双图案化及图案成型技术,以进一步推动制程工艺的前进。但是,EUV双图案化不仅成本高昂,且具有良率风险,所以需要具有更高分辨率光刻机来提供助力。

目前ASML正在开发的0.55 NA的High-NA EUV光刻机,分辨率为 8nm,能够帮助芯片制造商生产2nm及以下更先进制程的芯片,并且图形曝光的成本更低、生产效率更高。根据ASML的路线图,第一代的High-NA EUV光刻机TWINSCAN EXE:5000计划于2022年底推出,但这款机型可能主要是被晶圆制造商用于相关测试,实际量产的将会依赖于2024年底出货的TWINSCAN EXE:5200,每小时可生产超过220片晶圆。

当然,0.55 NA EUV光刻系统造价相比第一代的EUV光刻机也更高。据研究机构KeyBanc此前表示,一台0.55 NA EUV光刻系统的成本预计为3.186亿美元,而正在出货的0.33 NA EUV光刻系统则为1.534亿美元。

而根据ASML在2022年4月披露的信息显示,ASML在位于 Veldhoven 的新洁净室中已经开始集成第一个High-NA EUV光刻系统。2022年第一季度收到了多个EXE:5200系统(量产版High-NA EUV光刻系统)的订单,2022年4月还收到了额外的EXE:5200 订单。主要是来自三个逻辑厂商和两个存储厂商的 High-NA EUV订单。这里提到的三个逻辑晶圆厂应该是英特尔、台积电和三星,两个存储晶圆厂应该是三星和SK海力士。

△ASML首个High-NA EUV光刻系统

不过,根据ASML最新公布的信息来看,其High-NA EUV光刻系统的交付时间可能已经推后至2025年。

近期,ASML执行副总裁Christophe Fouquet在公开场合表示,自2010年代以来EUV技术越来越成熟,半导体制程微缩至2020年前后三年,以超过50%幅度前进。不过,速度可能会在2030年代进一步放缓。所以ASML计划2023年年底前发布首台商用High-NA EUV光刻机,并将于2025年量产出货。2025年开始,客户就能从0.33 NA EUV多重图案化,切换到0.55 High-NA EUV单一图案化,降低制程成本,提高产量。

总结来说,High-NA EUV技术是下一代(2nm及以下)尖端制程芯片制造的关键。此番美国纽约州携手美国及日本半导体大厂建立High-NA EUV半导体研发中心,主要目的就是为了进一步助力美国本土厂商提升在尖端半导体制程领域的设计和制造能力,而这也是美国芯片法案计划的延伸。

编辑:芯智讯-浪客剑

发布于:广东

相关推荐

EUV光刻机的全球战争

下一代EUV光刻机,万事俱备?

ASML:将按计划在年底推出首款High NA EUV光刻机

7大半导体巨头齐聚日本!美光斥资35亿美元建DRAM厂!IMEC将建研发中心!台积电、三星计划扩大投资!

下一代EUV光刻机即将爆发

EUV光刻机里的低调王者

ASML:我们有五个EUV光刻机客户

下一代光刻机,竞争激烈

投资风向悄然转变,腾讯减持Sea套现32亿美元意欲何为?

ASML光刻机是怎样一步步走上“绝路”的?

网址: 投资100亿美元!美国建High-NA EUV研发中心,意欲何为? http://m.xishuta.com/newsview101339.html