台积电造2纳米,创新生态如何提前布局

引人瞩目的台积电 2 纳米芯片,其开发生态已经接近完成。

上周,在欧洲举行的年度开放式创新平台论坛上,台积电(TSMC)向合作伙伴介绍了公司下一代代工技术路线图,其中尤为瞩目的是 2 纳米级 N2、N2P 和 N2X 工艺技术将在未来几年引入多项创新,包括环绕栅极纳米片(GAA)晶体管、背部供电以及超高性能金属-绝缘体-金属(SHPMIM)电容器。

尽管 N2 还有几年的时间,但许多主要的 EDA 工具、验证工具、基础 IP 以及 N2 的模拟 IP 都是全新的,芯片设计公司已经可以使用了。

所以 N2 芯片量产(计划在 2025 年下半年开始)的准备工作早已经启动。纳米片 GAA 晶体管的工作方式与人们所熟知的 FinFET 不同,因此 EDA 和其他工具和 IP 制造商必须从零开始构建其产品。这正是台积电开放式创新平台展示实力的地方,使合作伙伴能够提前开始着手其产品的工作。

Cadence 和 Synopsys 的主要 EDA 工具以及 Ansys 和Siemens EDA 的许多工具已经通过了台积电的认证,因此芯片开发商已经可以使用它们来设计芯片。此外,Cadence 和 Synopsys 的 EDA 软件已准备好用于模拟设计迁移。而且,Cadence 的 EDA 工具已经支持 N2P 的背后供电网络。

(编者注:美国已经提前禁止美国 EDA 公司的 GAA 技术用于中国企业,见未尽研究文章:芯片战,美国这次对中国断供的是 GAA EDA)

预构建的 IP 设计需要更长的时间。台积电的基础库和 IP 包括标准单元、GPIO/ESD、PLL、SRAM 和 ROM,已为移动和高性能计算应用准备就绪。同时,一些 PLL 存在于前硅验证套件中,而其他一些已经过硅化验证。

最后,诸如非易失性存储器、接口 IP 甚至芯片分组 IP 等模块尚不可用,这制约了一些芯片设计的进展。但根据台积电的演示,Alphabetwave、Cadence、Credo、eMemory、GUC 和 Synopsys 等公司正在积极开发或计划开发这些模块。总之,用于设计 2 纳米芯片的工具和库生态系统正在形成中,但还没有完全就绪。

台积电有一个开放创新平台(OIP),拥有一个大型工程团队,已经提前与 EDA 合作伙伴、IP 合作伙伴和其他合作开展工作。

2纳米背后的开放创新平台

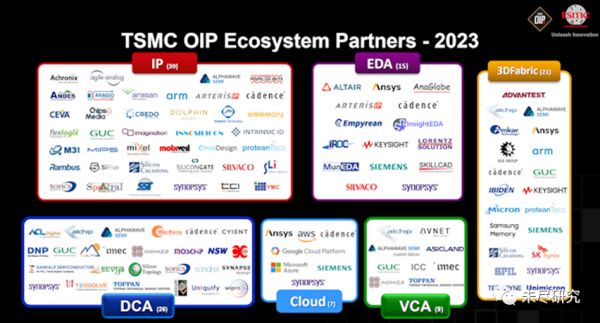

台积电今年正值开放创新平台成立 15 周年。这个平台汇聚了代工厂的供应商、合作伙伴和客户,帮助台积电的客户能更高效快速地实现芯片创新。开放创新平台现在涉及数十家公司和逾7万个用于各类应用的 IP 解决方案。它仍在不断发展。未来几年 2 纳米等新一代工艺技术和先进的封装方法成为主流时, 开放创新平台将发挥更加重要的作用。

台积电称之为“不仅仅是一个营销计划,实际上是一个使整个行业能进步的工程计划”。台积电设计基础设施管理负责人 Dan Kochpatcharin 在荷兰阿姆斯特丹召开的 2023 年 OIP 大会上表示,“我们拥有一个庞大的工程团队,与 EDA 合作伙伴、IP 合作伙伴和设计合作伙伴一起工作”。

缩短上市时间

缩短上市时间是台积电开放创新生态的出发点之一。在 2008 年开放创新平台出现之前,台积电需要大约 18 个月的时间开发一个工艺技术和工艺开发套件(PDK),然后将 PDK 和设计规则移交给电子设计自动化(EDA)软件和 IP 开发商等合作伙伴。后者将再花 12 个月的时间开发 EDA 工具和构建 IP 模块,然后再向芯片设计师提供方案和 IP 解决方案。接下来芯片开发商又需要 12 个月的时间来构建实际芯片。

通过开放创新平台,台积电的 EDA 工具和 IP 设计合作伙伴可以在台积电开始开发新工艺节点后的几个月内启动他们的产品开发。等台积电最终确定其工艺技术时,EDA 工具和 IP 已准备好可供芯片设计师使用。台积电认为这能缩短大约 15 个月的上市时间。这样,随着新节点的开发时间不断拉长,芯片的开发时间也在不断延长,台积电与 EDA 和 IP 提供商之间的提前合作的价值也在不断提高。

例如,台积电与其合作伙伴合作开发 2 纳米级(N2)的 EDA 和 IP 准备工作已经两年了,目标是在 2025 年下半年让工具和通用 IP 为芯片设计师准备就绪。

质量至关重要

台积电在选择加入开放创新平台的公司时非常挑剔,需要成员真正做出贡献,使共同努力成果大于各部分之和。由于台积电客户使用由开放创新平台参与者提供的 IP、软件和服务,后者必须在各自领域真正优秀才能成为开放创新平台的一部分。

事实上,台积电甚至有其 TSMC9000 计划(名称模仿 ISO9000 质量政策),为 IP 设计设置质量要求。IP 合作伙伴要经历 TSMC9000 评估,结果在 TSMC-Online 上公开,为客户提供 IP 可靠性和风险方面的指导。

在进行量产前,IP 提供商会首先完成 IP 设计的 tape out,即生成制造文件。然后使用这些文件进行 test shuttle,即试制一小批晶圆用于测试。之后他们会根据 TSMC9000 的检查表对 IP 进行评估。客户可以在 TSMC-Online 上看到所有的测试结果。这样就可以在量产前对IP的质量和正确性进行验证,以确保量产后的可靠性。

Kochpatcharin 解释道:“因此,客户可以看到,这个 IP 已经进行了硅化,因此他们对该 IP 更有信心。他们还可以看到有多少客户采用了该 IP,制片(流片)了多少次,量产了多少次。简而言之,这就是 IP 的消费者报告。”

联盟成员在台积电的一级目录中列出他们的 IP,包含 39 个贡献者提供的数千个 IP 选择。客户可以使用 TSMC-Online 设计门户上的“IP 中心”搜索 IP。目录中的每个 IP 都是由其原始合作伙伴开发、销售和支持的。同时,芯片开发商甚至可以用一个 IP 比较另一个 IP 的受欢迎程度,这可以让芯片开发商对其选择有更多信心。在当今封装越来越昂贵的情况下,信心是非常重要的,在 3 纳米、2 纳米和未来节点中将更加重要。

六大联盟

加快上市时间和确保质量并不是开放创新平台的唯一目的,它还旨在简化芯片的开发、生产、测试和封装。开放创新平台涉及各种成员,并组织成六个计划或联盟,每个负责一条工作条线:

IP 联盟,专注于提供经过硅化验证、量产验证和专为台积电定制的知识产权(IP),供其客户选择。

EDA 联盟,包括提供符合台积电技术要求并支持代工厂生产节点的EDA软件公司。

设计中心联盟,包括晶圆制造服务公司以及提供系统级设计解决方案的公司。

云联盟,汇集了 EDA 工具制造商和云服务提供商,使台积电的客户能够在云中开发和模拟芯片,以减少内部计算需求。

3D 封装联盟,汇集了所有负责先进封装以及多芯片制造商的公司,实际上包括所有上述公司以及存储器制造商(包括美光、三星和海力士)、基板制造商、OSAT 和测试设备制造商。

价值链联盟,类似于设计中心联盟,但旨在为广泛的客户(从创业公司和 OEM 到 ASIC 设计师)提供更广泛的晶圆制造服务和 IP 产品,以满足他们的需求。

3D 封装联盟项目去年底启动,所以可以认为是创新开放平台的最新补充。同时,3DFabric 联盟似乎正在快速扩张,这其中自有原因。

多芯片设计成为新标准

工艺技术正变得越来越复杂,这种情况不会改变。随着 Ansys、Cadence、Siemens EDA 和 Synopsys 等 EDA 制造商在其工具中加入人工智能功能,芯片设计工作流程未来可能会稍微容易一些。

但是由于高数值孔径 EUV 光刻机将曝光区域从 858 平方毫米减小到 429 平方毫米,看起来未来几年大多数 AI 和高性能计算(HPC)处理器将采用多晶圆设计,这将推动对支持多晶圆解决方案的软件、先进封装、HBM 类型内存以及全新测试方法等的需求。这将再次提高行业范围内协作及开放创新平台的重要性。

台积电从 2016 年开始提供 InFO_PoP 和 InFO_oS 3D IC,3D IC 已经量产多年,但早期它仍然是一个利基市场,只有很少客户可以做 3D IC。2021 年,台积电启动了 3DFabric,希望它对每个客户都通用,因为随着 AI 和 HPC 的到来,3D IC 不再是利基产品。例如,汽车是 3D IC 的一个有市场前景的应用领域。

与此同时,为实现下一代芯片和芯片间的连接,台积电设想需要硅光子技术,因此正在其开放创新平台中积极布局。

参考:

https://www.anandtech.com/show/21091/tsmc-ecosystem-for-2nm-chip-development-is-nearing-completion

https://www.anandtech.com/show/21086/importance-of-tsmcs-oip-is-growing-collaboration-needed-for-nextgen-chips

本文来自微信公众号:未尽研究 (ID:Weijin_Research),作者:未尽研究

相关推荐

台积电造2纳米,创新生态如何提前布局

台积电:2 纳米制程 2025 年量产,技术会领先全世界

台积电介绍3纳米和2纳米工艺进展,后者将于2025年投产

台积电预计6月将英伟达AI加速技术导入2纳米试产

知名科技博主:台积电要在美国设立5纳米晶圆厂,该如何解读?

台积电不要补贴,美国4纳米工厂发生火灾,外媒:这真是意外?

三星半导体死磕台积电:将放弃4纳米工艺直接过渡到3纳米

活在台积电阴影下的中芯国际,如何走向未来?

台积电们,都顶不住了?

台积电好≠电子大好,手机仍在砍单,电脑须防提前透支

网址: 台积电造2纳米,创新生态如何提前布局 http://m.xishuta.com/newsview94218.html