尴尬了!3nm芯片表现不及预期:良率低,提升还不明显

不管喜不喜欢今年的 iPhone 15,大概都会认可一件事,很多人选择购买 iPhone 15 Pro 系列的一大动机,就是冲着台积电 3nm 工艺的 A17 Pro。

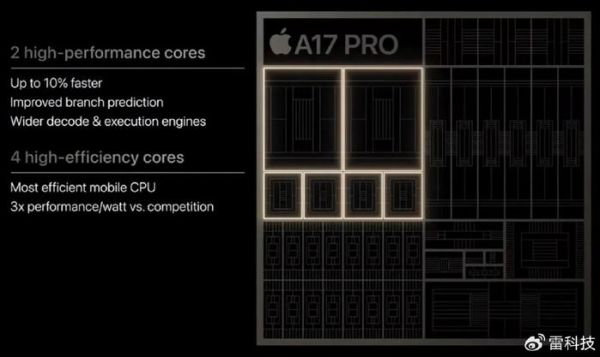

A17 Pro 采用了台积电最新的 3nm 工艺(N3B)制造,晶体管数量达到了惊人的 190 亿,这是全世界第一款采用台积电 3nm 工艺的手机芯片,也是 3nm 工艺第一次出现普通人就可以买到的大众消费品上。

要知道,随着芯片尺寸越来越逼近物理极限,每一代工艺节点升级需要投入也在加速增加,仅台积电一家的 3nm 新增投入就超过了 200 亿美元。

巨大的投入意味着巨大的成本,尤其是在前期工艺尚不成熟、良率较低的情况下,没有多少行业和公司能够负担 3nm 芯片的制造成本。

这其中,智能手机一直是最有实力和动力推动先进制程工艺不断前进的力量。

一方面是因为智能手机需要在极小的内部空间里塞下算力惊人的芯片,同时还要极可能降低芯片的功耗和发热;

图/苹果

另一方面是芯片制造太烧钱,也只有一年就能卖出十多亿台的智能手机可以形成规模效应,不断推动先进制程改进工艺、提高良率,得以让服务器、PC、游戏主机甚至是汽车用上更先进的芯片制造技术。

但更大的投入、更先进技术是不是就等同于「正确」?可能也未必,iPhone 15 Pro 系列的散热风波还没有过去,关于良率或者说成本的拷问,也一直是 3nm 上空的「乌云」。

良率和成本,3nm 的一朵「乌云」

10 月 9 日,《科创板日报》引述业内行业分析称,三星、台积电的 3nm 工艺良率目前都在 50%左右。一位接近三星的人士还透露,要赢得高通等大客户明年的 3nm 移动芯片订单,良率至少需要提高到 70%。

在半导体制造上,良率直接意味着一整片加工出来的晶圆上能正常工作的芯片的占比。通常来说,一片晶圆上可以同时制造出上百颗同样的裸芯片,之后将晶圆片上的裸芯片切割开来,就可以封装后安装到产品上。

图/台积电

在成熟工艺上,代工厂的良率一般都能达到 99%,但在先进制程上,由于工艺难度和前期的大量问题,良率就可能非常低。但按照惯例,代工厂并不负责承担不良芯片的制造成本,这部分费用还是由芯片设计客户承担,比如苹果、英伟达。

当然,「50%的良率」未必可信,此前就有大量各种来源的信息给出了各不相同的良率,包括 A17 Pro 从产业链传出的良率就为 70-80%。但这些消息无一例外,都透露出一个关键信息,即 3nm 的良率很低。

良率越低,成本越高。

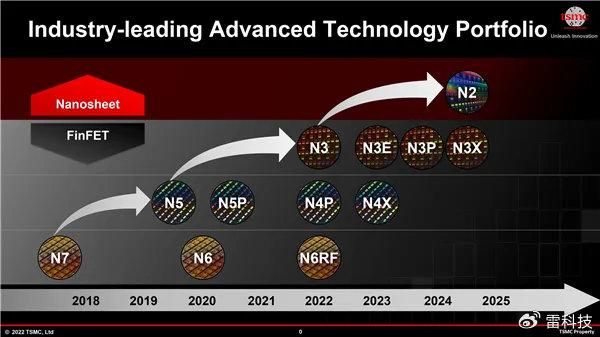

这也是为什么除了苹果,其他所有主要芯片设计公司都没有选择在 2023 年这个节点采用 3nm 工艺,更多还是瞄准 N3B 之后的工艺。按照台积电早前的规划,台积电 3nm 工艺其实是包括 N3B(即 N3)、N3E、N3P、N3X 等多个版本。

台积电制程路线图,图/台积电

甚至在业界传闻中,就连苹果也是与台积电签订了一份「对赌」协议,规定未来一年台积电 N3B 工艺为苹果专用,且废片均由台积电承担成本,而非苹果买单。

而如果说良率很大程度上决定了 3nm 的成本居高不下,进而提高了芯片设计公司导入的门槛,那 3nm 的功耗和发热问题,也是阻止他们较早导入的关键原因。

发热和功耗,3nm 的另一朵「乌云」

iPhone 15 Pro 系列的发热问题这里就不再赘述了,我们之前就在文章中分析,iPhone 15 Pro 系列发热的「罪魁祸首」就是设计和芯片两大部分,后者自然就是采用 3nm 工艺的 A17 Pro。

坦率地说,iPhone 15 Pro 的发热到底有多大程度是因为 A17 Pro,A17 Pro 的问题有多大程度是因为台积电 N3 工艺,目前来讲都还没有比较切实的论断。

但问题一定是有的。按照苹果给出的数据,A17 Pro 的晶体管数量为 190 亿,比前代 A16 增加了近 20%,CPU 性能却只提升了约 10%,GPU 核心数从 5 个增加到 6 个的同时,峰值性能提升了 20%。不过按照 GeekBench 数据来看,峰值性能大幅提高的另一面,是 A17 Pro TDP 峰值功率达到了惊人的 14W。

图/苹果

这不只是苹果和台积电面对的问题。

随着晶体管尺寸不断逼近物理极限,量子隧穿效应带来的问题也越发严重,失控的电子引发的漏电,会导致芯片更严重的发热和功耗问题。所以从 7nm 以后,整个业界的「制程焦虑」越发明显,对摩尔定律新出路的探索越发加快。

当然回到 3nm 上,台积电和三星也不是毫无准备的。

N3E 才是台积电真正的 3nm,三星押宝 GAA

相比 A17 Pro 上采用的 N3B 工艺,N3E 是台积电计划推出的一个完全不同的工艺节点,在功耗控制方面更加理想。

台积电不仅用上了「创新的阻挡工艺」,更重要的是 FINFLEX 技术的导入,让芯片设计人员可以在一个模组内混搭不同的标准单元,实现同时优化性能、功耗和面积。包括 N3P、N3X、N3AE、N3S 等工艺节点,实际都是 N3E 的后续变体。

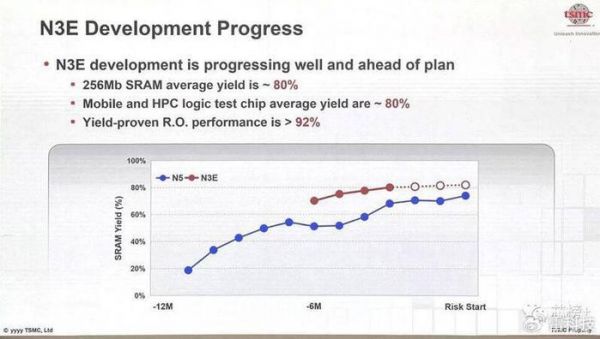

而且从过去半年的消息来看,普遍指出 N3E 的良率要好于 N3B,一份文件显示,N3E 256Mb SRAM 平均良率达到 80%,Mobile 与 HPC 芯片的良率也达 80%。此前,也一直存在台积电考虑放弃 N3B 节点,推迟到 N3E 节点正式进入 3nm 的传闻。

图/台积电

9 月 7 日,联发科与台积电共同宣布,联发科首款采用台积电 3 纳米制程生产的天玑旗舰芯片已经成功流片,该款天玑旗舰芯片将于 2024 年下半年上市。基本确定,这款天玑旗舰芯片(天玑 9400)采用了台积电 N3E 工艺,而官方透露:

台积电 N3E 工艺的逻辑密度相比 N5 工艺增加了约 60%,在相同功耗下速度提升 18%,或者在相同速度下功耗降低 32%。

相比之下,去年年末的 IEDM(IEEE 国际电子器件大会)上,台积电披露 N3B 工艺实际只将 SRAM 密度提高了约 5%(相比 N5 工艺),与其最初声称的 20% 也是相去甚远。

另外,9 月底业内又传出英伟达也下单了台积电 3nm 制程,以生产 Blackwell 构架 B100 数据中心 GPU,预计将采用更侧重性能增强的 N3P 或 N3X 工艺。

可以这么说,N3E 及其变种对于大多数芯片厂商来说,才是真正的 3nm。

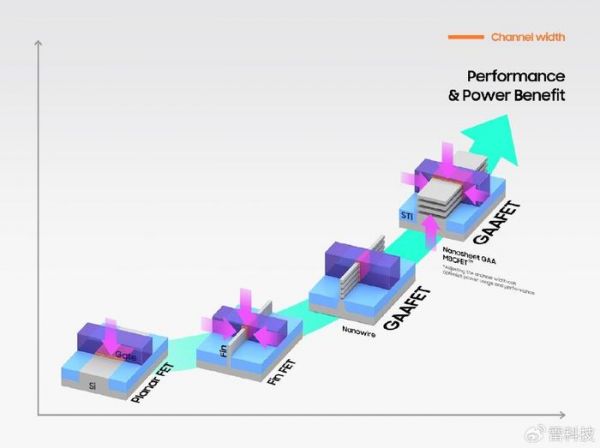

而在三星这边,去年 6 月就率先宣布了在 3nm 成功应用 GAAFET 技术。GAAFET 的正式名称是全环绕栅极晶体管(Gate-All-Around FET),架构上最明显的变化在单位面积内的利用效率。

晶体管架构变迁,图/三星

众所周知,计算性能最底层其实就是晶体管的「一开一关」,代表了二进制中的「0」和「1」,更底层是对晶体管内通道(又称沟道)的控制能力。FinFET 第一次将通道从横向转为竖向,而三星采用了宽通道(纳米片)的 GAAFET 技术,在单位面积内支持更多通道的控制,由此得以实现了:

与 5nm 工艺相比,第一代 3nm 工艺可以使功耗降低 45%,性能提升 23%,芯片面积减少 16%;而第二代 3nm 工艺则使功耗降低 50%,性能提升 30%,芯片面积减少 35%。(注:三星第二代 3nm 也要等到明年。)

相比台积电还在用的 FinFET 技术,GAA 拥有更好的静电控制能力。法国信息技术电子实验室高级集成工程师 Sylvain Barraud 也指出:「与 FinFET 相比,GAA 堆叠的纳米线还具有更高的有效沟道宽度,能够提供更高的性能。」

事实上,台积电和英特尔也早早宣布将在 2nm 节点正式导入 GAA 技术,之所以没有在 3nm 节点,主要顾虑还是技术成熟度不高带来的良率问题,三星 GAA 3nm 此前就多次传出严重的良率问题,甚至是在宣布量产后找上美国 Silicon Frontline Technology 公司,合作提高 3nm GAA 工艺的良率。

所以对三星来说,关键还是在于保持 3nm GAA 能效优势的同时,如何尽可能地提高良率。

硅晶圆,图/三星

写在最后

时至今日,所有人都明白,在物理尺寸上极其微小的芯片,在现实世界是何等的重要,而芯片上的每一寸进步,实质上也会推动全世界算力的大幅提升,这也是过去几十年人类科技进步的主要动力之一。

与 1nm 之后的未来相比,3nm 目前遇到的问题既不困难也不意外,晶圆厂早就有所预想和准备。但即便是芯片制程无限逼近物理极限的几年后,从来也没有什么无解的问题。

大规模集成电路兴起的时候,糟糕良率一度让很多公司失去了信心,但还是仙童半导体、德州仪器等公司将芯片制造车间换成了无尘的超净间,进入的人都要穿上极其严密的防护服,确保灰尘、汗液和毛发不会损坏脆弱的晶圆,实现了足够高的良率。

MOS 管(场效应晶体管)接近性能极限的时候,很多人也认为晶体管不能再变小,芯片性能提升到了尽头。但最终,FinFET 架构继续推动了芯片技术的前进。

2019 年,在台积电内部举办的运动会上,台积电创始人张忠谋被媒体问到了摩尔定律是否走到尽头时,他认为这个问题的答案,沒有人知道,因为后面至少还有 5nm、3nm 和 2nm 的技术。但他相信,摩尔定律的未来会是:

山穷水尽疑无路,柳暗花明又一村。

题图来自苹果

发布于:广东

相关推荐

尴尬了!3nm芯片表现不及预期:良率低,提升还不明显

报告称三星 3nm 芯片良率已超过台积电

台积电、三星的3nm实际良率都只有50%左右!

3nm芯片,台积电的一道小坎

苹果3nm芯片计划背后

3nm,台积电的一道小坎

芯片制程:28nm向3nm的“大跃进”

消息称苹果下巨额3nm芯片订单,要求台积电承担未合格芯片成本

台积电与苹果“对赌”3nm芯片,和三星决“生死”

消息称台积电 3nm 工艺 A17 Bionic、M3 良率仅 55%……

网址: 尴尬了!3nm芯片表现不及预期:良率低,提升还不明显 http://m.xishuta.com/newsview93545.html