三星和佳能们,找到了一个“备胎”

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:L晨光,原文标题:《纳米压印,终于走向台前?》,题图来自:视觉中国

现如今,ASML几乎成了光刻机的代名词。尤其是随着EUV、甚至High-NA EUV光刻机的推出,ASML更是独霸高端光刻机市场。

众所周知,光刻是芯片制造过程中最重要、最复杂也最昂贵的工艺步骤,其成本占总生产成本的30%以上,同时占据了将近50%的生产周期。

数十年来,在DUV、EUV光刻机的支持下,摩尔定律得到了延续。然而,迭代至今,面对芯片晶体管线宽已趋近物理极限,以及EUV光刻机产能有限、成本高等问题,业界开始加强探索绕开EUV光刻机生产高端芯片的技术和工艺。

其中,纳米压印技术(NIL)走到了台前。

近日,有消息披露,SK海力士从佳能引进了纳米压印设备,目前正在进行测试,计划在2025年左右使用该设备开始量产3D NAND闪存,到目前为止的测试结果良好。

这里提到的纳米压印技术,就是被认为最有可能替代EUV的下一代光刻技术。

纳米压印技术如何对标EUV光刻?

纳米压印技术,即Nanoimprint Lithography(NIL),是一种新型的微纳加工技术。该技术将设计并制作在模板上的微小图形,通过压印等技术转移到涂有高分子材料的硅基板上。纳米压印的分辨率由所用印模板图形的大小决定,物理上没有光刻中的衍射限制,纳米压印技术可以实现纳米级线宽的图形。

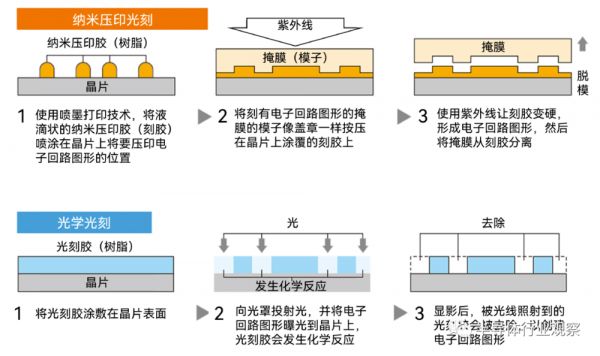

紫外纳米压印光刻与光学光刻流程对比(图源:果壳硬科技)

可以理解为,纳米压印技术造芯片就像盖章一样,把栅极长度只有几纳米的电路刻在印章(掩膜)上,再将印章盖在橡皮泥(压印胶)上,实现图形转移后,然后通过热或者UV光照的方法使转移的图形固化,以完成微纳加工的“雕刻”步骤。

纳米压印替代的是光刻环节,只有光刻的步骤被纳米压抑技术代替,其他的刻蚀、离子注入、薄膜沉积这些标准的芯片制造工艺是完全兼容的,能很好地接入现有产业,不用推翻重来。

光刻技术的本质是掩膜版用于对光刻胶进行图案化,从而实现图案化沉积和蚀刻工艺。光刻工艺的最终分辨率由所用光源的波长决定。

而如今业界依赖的光学光刻存在诸多局限性:

SDAP、SAQP工艺是二维图案化解决方案,严重限制了设计布局;

由于精度有限,想要将更精密的芯片线路曝光出来,还需要采用多重曝光技术;

提高光学光刻分辨率主要通过缩短光刻光源波长来实现,尽管光源已从紫外的436nm、365nm缩短到深紫外(DUV)的193nm和极紫外(EUV)的13.5 nm,但在光学衍射极限限制下,分辨率极限约为半个波长;

光刻光源波长缩短使得光刻设备研制难度和成本成倍增长,其成本与规模化能力已无法与过去25年建立的趋势相匹配。

因此,业界开始寄望于纳米压印光刻技术。

在芯片制造中引入的任何新光刻技术,都必须提供性能优势或成本优势。

与传统的光刻技术相比,首先,纳米压印技术不需要复杂的光路系统和昂贵的光源,可以大幅降低制造成本。

另外,纳米压印的模板比光刻机用的掩膜版图案设计更简单,压印出来的图案尺寸完全由模板上的图案决定,所以不会受到传统光刻胶技术中光源波长、光学衍射的限制和影响。与光刻设备产生的图案相比,纳米压印技术忠实地再现了更高分辨率和更大均匀性的图案。

同时,纳米压印技术只要预先在掩膜上制作好图案,即使是复杂结构也能一次性形成,同时也避免了传统光刻工艺中的多次重复曝光,进一步提升了成本优势。据日经中文网报道,纳米压印能省掉成本巨大的光刻工序的一部分,与极紫外光刻相比,能将该工序的制造成本降低4成,耗电量降低9成。

此外,纳米压印技术在三维立体结构加工方面有着它独特的优势,传统的光刻技术都是基于二维平面的加工方式,三维结构获取比较困难,同时可控性较差,但是对于纳米压印技术,只要制作成模板,就可以批量生产三维产品。

纳米压印技术,突破与挑战并存

1995年,华裔科学家周郁(Stephen Chou)教授首次提出纳米压印概念,从此揭开了纳米压印制造技术的研究序幕。

到2003年,纳米压印作为一项微纳加工技术,被纳入国际半导体技术蓝图(ITRS)。

2009年,美国从事纳米压印基础技术研发的Molecular Imprints公司(MII)曾规划将NIL技术用于32nm逻辑节点生产制造。但进展也未及预期——据说是因为生产速度慢,而且缺陷率高,资金问题也成为MII发展技术的掣肘。

五年后的2014年,佳能收购了MII。实际上,早在十年前,佳能从2004年就开始一直秘密研发纳米压印技术,直到收购MII公司,将其更名为Canon Nanotechnologies,从而进入NIL市场。

此后,佳能与东芝联合开发NIL技术——东芝(2019年,东芝储存器改名为铠侠)很早就想将NIL用在平面NAND闪存制造上。不过似乎193nm光刻和多重曝光就能将NAND单元尺寸从120nm缩减到1xnm节点;然而到这个节点,原有工艺就很难再实现存储单元和浮栅的微缩。

因此,NAND开始向3D化演进,东芝对于NIL技术的应用也有了转向。大约五六年前,东芝称非易失性存储器件的光刻需求,正从更高分辨率走向更低的成本,所以计划在3D NAND时代应用NIL。

也大概是自此之后,一直有佳能将纳米压印技术用于量产存储芯片的新闻。

据了解,佳能最新的纳米压印设备的参数指标不错,套刻精度为2.4nm/3.2nm,每小时可曝光超过100片晶圆,纳米压印技术已经达到3D NAND大规模生产水平和要求。

上文也提到,除了铠侠之外,SK海力士也从佳能购买了纳米压印设备,正在进行用于3D NAND型闪存生产工程的测试,这也被认为是业界最尖端制造工艺中使用的EUV光刻机的下一代设备。

有业内人士表示:“与EUV相比,纳米压印技术形成图案的自由度较低,因此预计将优先用于生产维持一定图案的NAND型闪存。”SK海力士开始采购设备也是因为这个原因。”

如果纳米压印设备实现商用化,以SK海力士为首的NAND闪存企业将能够提高从200层开始的工序难度越来越高的3D NAND闪存领域的生产效率。

另一方面,存储芯片巨头三星电子也为了解决引进多图案工艺导致的成本上升问题,迅速导入了EUV光刻机,除此之外还开发了包括纳米压印技术在内的3-4种解决方案。

除了在NAND闪存领域的探索外,佳能正在尝试将NIL技术应用到DRAM和CPU等逻辑芯片上。

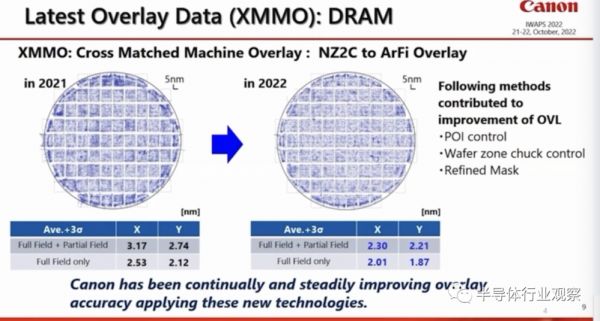

针对DRAM方面,佳能一直在不断改进套刻精度。使用POI 控制技术、晶圆区卡盘控制、精细掩膜等方式有助于改善套刻精度。

图源:佳能

高级的NIL工具和掩膜相结合可以为许多不同的应用提供多种解决方案,佳能展示了2.3nm套刻精度应用于各种新技术,主要用在DRAM方面。

在芯片领域,纳米压印光刻更擅长制造3D NAND、DRAM等存储芯片,与微处理器等逻辑电路相比,存储制造商具有严格的成本限制,且对缺陷要求放宽,纳米压印光刻技术与之较为契合。

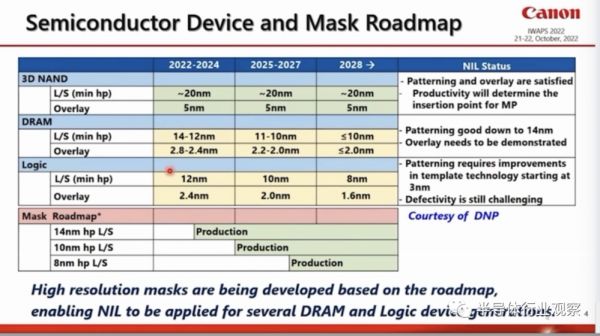

据佳能在纳米压印设备未来路线图显示,应用将从3D NAND存储芯片开始,逐渐过渡到DRAM,最终实现CPU等逻辑芯片的制造。

图源:佳能

据了解,佳能目前量产的纳米压印设备,能用于生产15纳米的芯片,预计到2025年,能进一步研发出生产5纳米芯片的设备。初期将率先导入生产NAND、DRAM等,未来还有望导入应用在PC和手机中的需要高阶先进制程的逻辑IC生产。

为了实现这一目标,佳能日前在法说会上提出将在日本斥资逾500亿日元,扩增其微影设备产能,佳能表示该厂房将于2023年兴建,预计从2025年开始营运。该工厂除了生产其现有的光刻机系列产品,还将生产纳米压印光刻设备。

此前,佳能和铠侠、DNP(大日本印刷)在纳米压印技术上就有了不少的合作。DNP 2015年据说是建立了纳米压印模板(template)的商业化生产系统;而东芝是2016年宣布计划用纳米压印来制造NAND闪存。

可见,从设备试产、晶圆厂试运行,再到新厂生产线投产设备,日企欲通过半导体“纳米压印技术”来追赶ASML的脚步。

此外,目前这一技术方向的其他设备供应商还包括Nanonex、EVG、SUSS MicroTec、Obducat等欧美公司。

EVG公司日前宣布与凸版印刷分拆成立的光掩膜子公司Toppan Photomask合作,共同开发NIL 技术,进一步加速其在光学微纳制造领域的应用。纳米压印工艺设备提供商与纳米压印母版制造商之间的首次合作是该行业的巨大成就,将帮助行业迅速扩大纳米压印作为先进光学设备的大规模生产技术和组件。

从1995年至今,经过不断的改进和技术突破,纳米压印技术已经被应用到LED、屏幕显示、DNA测序、AR/VR、传感等领域。

但应用于集成电路制造,尚处于产业化初期阶段。目前,纳米压印技术在ITRS中被列为下一代32nm、22nm和16nm节点光刻技术的代表之一。经过近30年的研究,纳米压印技术已经在许多方面有了新进展,国内外半导体设备制造商、材料商以及工艺商纷纷开始涉足这一领域。

芯片制造领域,纳米压印技术挑战仍在

虽然前面提到了不少纳米压印技术的优势,甚至被奉为新的行业希望,但是纳米压印技术距离大规模商业化量产还有一些短板没有补足。

良品控制:纳米压印由于是晶圆和掩膜直接接触,容易出现电路上混入细小垃圾和灰尘等的残次品,要实现实用化,必须进行制造技术和运用方面的改良。

模板寿命低,更换成本高:不管是DUV光刻、EUV光刻还是纳米压印,最贵的耗材都是掩膜版或者压印模板。纳米压印的模板,因为是需要直接接触压印胶工作的,在接触的过程中,难免会有各种各样的损伤或者污染,缩短模板寿命。

对准复杂:压印模板需要与承载压印胶的基台精确对准与贴合,需要精密的机械装置配合检测设备实施压印过程。然而现有纳米压印设备在平行与垂直对准方面缺少高精密的调准机构。虽然我们可以沿用紫外光刻上的光学对准或者莫尔条纹技术做对准,但是纳米压印不仅有固化,还有垂直方向的压印运动过程,所以会带来多方向的偏差。

这几个问题,其实不能全说是纳米压印技术的问题,降低工艺成本、提高良品率和提高生产效率对于发展初期的光刻机来说也是同样要面对的问题,任何一项技术从实验室走向成熟,都会面对这些问题,都需要在发展过程中解决这些问题。

NIL能否替代EUV光刻?

回顾芯片光刻产业历程,21世纪的前20年里,由于全球芯片产业链条在浸入式DUV、EUV等投影式光刻技术的持续巨大投入,投影式光刻成为IC制造的主流技术,诞生了荷兰ASML光刻设备巨头,以及应用层面的台积电、三星等国际芯片加工企业,纳米压印光刻逐渐退出IC制造技术的竞争,进入沉默期。

而随着产业向前发展,DUV、EUV光刻机等系统复杂度、技术瓶颈和成本问题等日益突出,纳米压印技术似乎又迎来了新的目光。

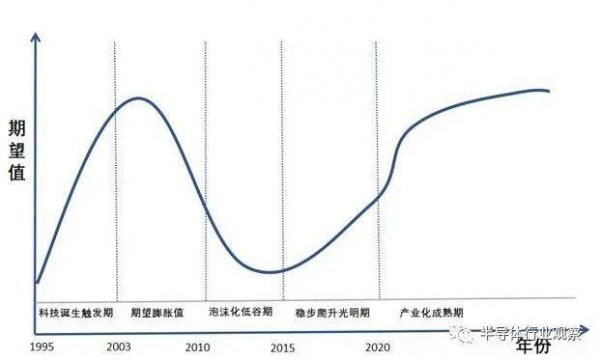

根据Gartner提出的新科技技术成熟度曲线,综合技术发展历程中的专利、论文、市场情报等数据,以年度和期望值维度,绘制了纳米压印技术产业化曲线。

纳米压印技术产业化曲线

科技诞生触发期:自1995年纳米压印技术提出后,引起学术界和产业界广泛关注和跟进,目前领先的技术和设备提供商大多在这一阶段进入。

期望膨胀期:2003年,纳米压印技术首次纳入国际半导体蓝图(ITRS),技术的研究和期望进入高潮,这一时期,纳米压印相关设备被科研机构大量采购。

泡沫化低谷期:受制于工艺不成熟,产业化不及预期。一批企业倒闭或被收购,标志性事件是2014年佳能收购MII。但是这段时间,纳米压印大面积、连续生产的相关技术被开发出来,在生产光子晶体LED芯片领域实现产业化。

稳步爬升光明期:技术工艺逐步突破,在LED、微流控、MEMS、AR等领域实现产业化应用。国内企业也加大纳米压印技术的研发和应用布局。

产业化成熟期:2021年后,随着工艺成熟和下游应用领域的突破发展,纳米压印技术或将迎来大面积产业化。

TechNavio数据显示,2026年纳米压印市场有望达到33亿美元,2021年至2026年年复合增长率可达17.74%。纳米压印市场虽然没有想象中那样大,但整体正逐渐走强。

纳米压印技术有着其独特的优势,也有相对应的缺点,在未来的科研生产中,需要进一步的优化工艺条件,帮助拓展改进纳米压印技术的应用。

最后回到本篇内容的核心——在芯片制造领域,虽然日本最早完成实践,但能否替代EUV光刻呢?

老实来讲,难度是非常大的,除非台积电、三星、英特尔、SK海力士等行业大厂放弃成熟技术转战纳米压印技术。其实从行业动态也能看到,每隔几年都会有纳米压印光刻即将突破的消息,但每次又延后进入产业的时间。

一切信号都在表明这项技术的发展有很多难关。但未来,当光学光刻真正达到极限难以向前时,纳米压印技术或将是一条值得期待的路线,而那时,芯片制造或许也会迎来全新的范式,一切都会被颠覆。

毕竟,没有一种技术能够长期存在,倘若有,那也只是因为人们还没有来得及发现新的东西来取代它而已。

本文来自微信公众号:半导体行业观察 (ID:icbank),作者:L晨光

相关推荐

三星和佳能们,找到了一个“备胎”

佳能32年:数码相机寒冬,电动车续命

不止华为,谷歌、亚马逊、阿里都有芯片“备胎”计划

300亿收购芯片厂,佳能还能继续“感动常在”吗?

原来华为是这样养“备胎”的

台积电和三星都变脸了,美国图谋失败,外媒:拜登心都碎了

鸿蒙“备胎扶正”,华为背水一战

“主力”和“备胎”: 家电巨头IoT时代的两难

在加价中杀出重围,佳能R8购买思路分享

欧拉为什么不可能是华为的“备胎”?

网址: 三星和佳能们,找到了一个“备胎” http://m.xishuta.com/newsview74410.html