ASML的EUV光刻之路还能走多远?

虽然近期台积电高管表示,台积电接下来的A16/A14制程都不会采用ASML售价高达4亿美元的High NA EUV光刻机(具有0.5数值孔径),但是英特尔则已经决定在其下一代的Intel 14A制程上选择采用High NA EUV光刻机进行量产。

与此同时,为了解决1nm以下制程的制造问题,ASML正在积极研发具有0.75NA的Hyper NA EUV光刻机,这也意味着其将面临更大的技术挑战,要知道,ASML花了约20年的时间才成功推动标准型EUV光刻机的规模化商用。

而作为急需在EUV光刻机上进行突破的中国,则将目光瞄向了基于直线电子加速器的自由电子激光技术的EUV光源(EUV-FEL)技术。

EUV光刻机:17年的时间和90亿美元的研发投入

目前,全球几乎所有的7nm以下的制程工艺都全面采用了ASML的EUV光刻机来进行量产,同时随着DRAM制程进入到10nm,美光、三星、SK海力士等存储大厂也开始或计划导入EUV光刻机。

虽然上一代的193nm浸没式光刻机采用多重曝光技术将制程工艺推进到7nm左右(极限甚至可以到5nm,但是良率会大幅降低),但使用多重曝光会带来两大新问题:一是光刻加掩膜的成本上升,而且影响良率,多一次工艺步骤就是多一次良率的降低;二是工艺的循环周期延长,因为多重曝光不但增加曝光次数,而且增加刻蚀(ETCH)和机械研磨(CMP)工艺次数等,这也会带来成本的大幅上升和良率的降低。

而要解决193nm浸没式光刻所面临的问题,最为有效的方法就是进一步缩短光源波长,来提升光刻分辨率。因此,在20多年前,头部的晶圆制造商和ASML就将目光瞄向了光源波长只有13.5nm的EUV(极紫外光)光刻技术。

1997年,英特尔牵头创办了EUV LLC联盟,随后ASML作为唯一的光刻设备生产商加入联盟,共享研究成果。随后,ASML通过一系列的收购(比如收购美国准分子光源提供商Cymer等)和自身的研发,在2010年首次推出了概念性的EUV光刻系统NXW:3100,但是直到2016年面向量产制造的EUV系统NXE:3400B才开始批量发售,从而真正开启EUV光刻系统的新时代。

据ASML此前介绍,在EUV光刻机的研发上,ASML总计花了90亿美元的研发投入和17年的研究,才最终获得了成功,最终到进入大规模商用更是花了约20年的时间。

相对于193nm浸没式光刻机,EUV光刻机不仅可以使得光刻的分辨率大幅提升,同时一次就能曝出最小距离为13nm精细图形,而且不需要浸没系统,没有超纯水和晶圆接触,在产品生产周期、OPC的复杂程度、工艺控制、良率等方面的优势明显。当然,唯一的劣势在于最初的价格高达1.5亿美元一台。

凭借着英特尔、台积电、三星这三大头部先进制程客户的强力支持,再加上ASML自身在EUV光刻领域的持续研发投入,以及在EUV光刻设备上游的关键器件和技术领域的多笔收购及投资布局,使得ASML多年来一直是全球EUV光刻机市场的唯一供应商。

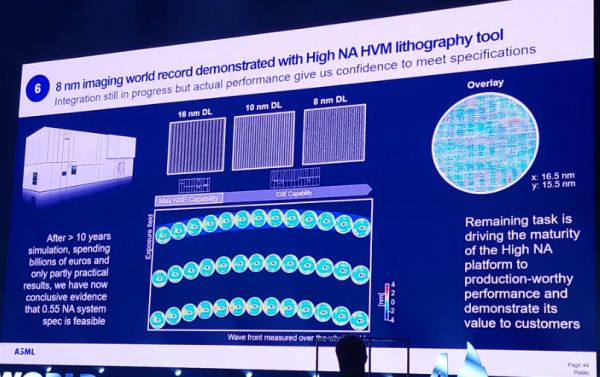

领导ASML研究部门的Jos Benschop说:“几十年来,在摩尔定律的推动下,过去每一代新的制程节点的晶体管长度和宽度都缩小了70%。但是现在每一代微缩的幅度已经降低到了大约20%。”虽然现在最先进的High NA EUV光刻机可以打印8nm的线条,距离大约为32个硅原子。但当晶体管间距靠得如此近时,量子隧穿效应就可能会出现——电子可能将表现出不可预测的行为。

自上世纪90年代末以来,一直从事EUV研究的Benschop说:“根据最初的缩放比例,我们将在2065年左右达到四分之一纳米(2.5埃米)的水平,即两个硅原子之间的距离。但是,根据现在的预计,我们可能会在下个世纪中叶才达到那个点。”因此,在未来几十年中,ASML可以继续尽可能高效地缩小晶体管的尺寸。但是,怎么做到这一点呢?

携手ARCNL

据荷兰媒体NRC报道,ASML除了自身投入大量的资金进行技术研发之外,也在与阿姆斯特丹纳米光刻高级研究中心(ARCNL)开展合作。

据介绍,ARCNL成立于十年前,与阿姆斯特丹大学的合作伙伴关系。推动者是ASML的前技术总监兼联合总裁Martin van den Brink,他已于去年退休。ASML公司支付了ARCNL预算的三分之一(每年约400万欧元),以便80名科学家可以研究前沿的光刻技术的构建模块。

ARCNL的任务是改进ASML现有的EUV光刻技术,并在未来EUV失败的情况下研究替代方法。

Wim van der Zande自2022年以来一直担任ARCNL的董事,之前曾在ASML的研究部门工作。学者们与费尔德霍芬和圣地亚哥的ASML研究人员以及荷兰和国外的技术大学合作。“这是一个完整的生态系统。”Van der Zande说。

ARCNL在与ASML相关的领域进行研究,该公司是第一个有机会评估新想法的公司。这种合作让人想起NatLab。这个前飞利浦实验室做出了CD播放器等著名发明,也为ASML的光刻技术奠定了基础。NatLab进行了开创性的研究,即使它没有直接的商业应用,最终被飞利浦削减。

ARCNL的科学家们意识到ASML最重要的挑战:经济可行性。毕竟,不为芯片制造商赚钱的机器是不会有什么买家的。ASML目前每年在研究方面的投资超过40亿欧元,远高于其他荷兰公司,因此它可以将ARCNL纳入自己的管理之下。但这种做法将有损于开放的学术研究。

Van der Zande表示:“作为一名科学家,你可以花很多年时间进行一项研究,但商界只关注短期回报,可能会因此突然停止一个项目。”尽管如此,大约四分之三的ARCNL研究人员在获得博士学位后继续在ASML工作。

更短波长的光源

1984年,当ASML创立时,光刻机使用波长为365或436nm的汞灯作为光源。随后是248纳米和193纳米的激光。数年前已经跃升至13.5nm的EUV光源。

目前,科学家们正在寻找合适的6.7nm和4.4nm波长光源。有一些元件可以为EUV反射镜提供透明度和反射的正确组合——对于6.7纳米,这些材料是羊毛甾烷和硼。缺点:在较短的波长下,反射效果较差。

为产生6.7纳米的光,ARCNL正在构建一个使用钆而不是锡的研究装置。然而,较短的波长并不是万能的。能量分布在较少的光子上,如果您想打印纳米级的线条,这会增加出错的风险。用技术术语来说:会有随机噪声。“总而言之,我认为我们进入更小波长的可能性很小。”Benschop说。

更大的数值孔径

光刻机分辨率的提升除了可以依赖于缩短光源的波长之外,还可以通过提升镜头的数值孔径(NA)来实现。目前的EUV光刻系统的数值孔径是0.33 NA,而ASML最新推出的High NA EUV系统的数值孔径已经提升到了0.5 NA。

为此,ASML的合作伙伴蔡司(Zeiss)不得不使用直径超过一米的更大物镜,同时,蔡司还必须开发复杂的测量设备,以将物镜的误差降低到低至原子的偏差(其实早在2016年11月5日,AMSL就收购了卡尔蔡司半导体制造技术公司(Carl Zeiss SMT)的24.9%股权,以强化双方在半导体微影技术方面的合作,研发High NA EUV光刻系统)。

ASML及其镜头供应商蔡司要想推动High NA EUV商用,还必须联合供应链做出更多的妥协。

首先,High NA EUV的芯片图案所在的视场较小。因此,较大的芯片设计必须切成两半,然后再重新绑在一起,这很麻烦。

其次,High NA EUV虽然分辨率更高,但焦深较小。这需要调整光敏涂料,它必须具有不同的化学成分,并且必须涂得特别薄(小于20纳米)。

第三,晶圆本身也必须特别平坦,以防止偏差。

在High NA EUV成功推出的同时,ASML和蔡司还在研究新一代数值孔径为0.75 NA的Hyper NA EUV光刻系统。

Jos Benschop表示,Hyper NA EUV光刻系统的物镜并不一定非得更大,“你也可以把最后一面镜子放在离芯片更近的地方,这样你就会得到同样的效果。缺点是更多的光线会反射回来——这就是镜子的情况。”

Hyper NA EUV还有一个优点,更大的数值孔径可以处理更多的光线,就像你倒空宽颈的瓶子比清空窄颈的瓶子更快。因此,Hyper NA EUV不仅能够打印出更清晰的线条,而且打印速度也更快。

根据Martin van den Brink此前披露的ASML未来15年的逻辑器件工艺路线图,利用目前的0.3NA的标准型EUV光刻机支持到2025年2nm的量产,再往下就需要通过多重曝光技术来实现,但支持到2027年量产的1.4nm将会是极限。

而0.55NA的High NA EUV光刻机则可以支持到2029年1nm制程的量产,如果采用多重曝光,则可以支持到2033年量产的5埃米(0.5nm)制程节点。

再往下就可能必须要采用0.75NA的Hyper NA EUV光刻机,或许可以支持到2埃米(0.2nm)以下的制程节点,路线图在这里打了一个问号,所以,不确定Hyper NA EUV光刻机能否支持下去。根据ASML的规划,Hyper NA EUV光刻机首款产品可能会在2030年前后推出。

这里需要强调的是,虽然一个硅原子的直径就在1埃米左右,但是这里的所有的制程节点命名都只是等效指标,并不是真实的物理指标。2埃米制程节点的对应的晶体管的金属间距为大约在16~12nm,进入2埃米制程以下时,金属间距才会进一步缩小到14~10nm。

所以,Benschop才会说,预计到下个世纪中叶,晶体管之间的间距才有可能进一步缩小到1/4 nm的水平。

更高的EUV光源功率,更低的能耗

目前,ASML的EUV光源(被称为激光等离子体光源),是利用德国通快(Trumpf)公司30千瓦功率的二氧化碳激光器,每秒2次轰击雾化的锡(Sn)金属液滴(锡金属液滴以每秒50000滴的速度从喷嘴内喷出,即每秒需要10万个激光脉冲),将它们蒸发成等离子体,通过高价锡离子能级间的跃迁获得的13.5nm波长EUV光线。然后,ASML对EUV光进行收集,并通过反射镜修正光的前进方向,最终进入镜头,作用到芯片表面的光刻胶。

△ASML EUV光源的微型版本

由于EUV光线波长非常短,所以它们很容易就会被空气吸收,因此,整个EUV光源的工作环境需要被抽成真空。同时,EUV光线也无法被玻璃透镜折射,必须通过蔡司用硅与钼制成的特殊镀膜反射镜,来修正光的前进方向,而且每一次反射可能将会损失约30%的能量,EUV光学照明系统中有6组反射镜,这就导致最终到达晶圆表面光阻层的EUV光源功率理论上只有原来的约1%左右。

相关资料显示,在2015年,ASML才设法将EUV光源提升到了100W,其庞大的drive laser(驱动激光器)加上其他部分,使得整个EUV光刻机的功耗达到了惊人的15000KW。

现在,ASML已经将EUV光刻机的EUV光源功率提升到了500W,接下来ASML计划进一步将功率提升到1000W,同时ASML希望持续降低能耗。ASML预计,到2033年,每个照射晶圆的EUV能耗将比2018年减少约80%。

如何来实现这些目标呢?据NRC称,ASML计划将每秒喷射的50000滴锡金属液滴提升到60000个,从而提升产生的EUV光源功率。另外,为了更有效地利用Trumpf公司的激光器,ASML希望drive laser使用固体激光器,因为它将消耗更少的能量。ARCNL也曾建议使用固体激光器来降低能耗。

“夹层蛋糕”式反射镜

如前所述,目前ASML的EUV光线利用蔡司的特殊镀膜反射镜修正光的前进方向,每一次反射可能将会损失约30%能量,这也意味着,如果经过10面反射镜,可能只剩下不足3%的能力。而ASML的High NA EUV如果采用了相对较少的反射镜,那么可以作用于晶圆表面光刻胶的EUV光源功率会更高。但是,如果反射镜更少,可能就很难纠正镜头误差。

NRC称,特温特工业大学的研究人员正在研发新的镜面涂层,该涂层由一堆交替的钼和硅层组成,一种材料可以反射EUV光线,另一种则是透明的,总共有大约70个“多层”相互重叠,每个层的占比略低于3%。

“我们现在实现了高达71%的反射率,接近理论上可以达到的75%。”Marcelo Ackermann教授说。他领导XUV Optics小组,与蔡司和ASML合作研究涂层配方。该实验室建立在Fred Bijkerk教授于1990年代初在Nieuwegein的FOM研究所开始的EUV研究的基础上。

计算似乎很简单:反射层的厚度必须达到波长的一半。诀窍在于精确的构图和每层仅10nm厚的整齐分层。这是通过一种被Ackermann称为“微波溅射”的方法完成的。与最早的EUV反射镜相比,这种“夹层蛋糕”式的反射镜的各层现在彼此之间更加紧密地分离,更有利于光输出。

Marcelo Ackermann教授的实验室与ARCNL一起,还为在EUV水平上生长的囊泡找到了解决方案。诀窍是添加额外的材料。“至于选择哪种材料?这就是我们的秘方。”Marcelo Ackermann说。

更大、更快的掩膜版

此外,High NA EUV光刻机使用镜子,以不同的方式在长度和宽度上放大掩模板上刻画的芯片图案的蓝图。因此,在晶圆上刻画芯片图案就需要更长的时间。ASML则希望通过提高速度来补偿这一点。

现在,在High NA EUV光刻机的顶部,像复印机扫描仪一样来回移动的掩膜版支架,其加速度达到了32G,也即重力的32倍。Benschop说,只要机器不发生故障,就可以再快几倍。

现在的大型AI芯片包含数千亿个晶体管和数十个处理器内核,设计非常大,因此它们不再适合使用High NA EUA光刻机来一次完成一个传统的掩膜板图案的光刻。所以,目前AI芯片的制造依赖于各个部分单独光刻,然后通过先进封装技术整合在一起。这虽然也很有效,但不方便。

如果芯片制造商愿意,ASML可以切换到更大尺寸的掩模,从而再次“用画笔绘画”。然后,英特尔和台积电等各方必须带头说服口罩行业的供应商。

进行更多测量

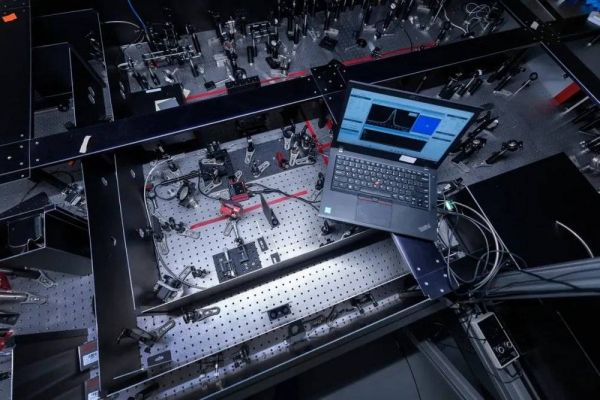

EUV光刻可以写入纳米结构,也可以测量它们。戴着护目镜的Stefan Witte教授正在ARCNL工作,主要研究法国物理学家Anne L'Hullier诺贝尔奖获奖研究的应用。她发现,超短光脉冲就像乐器一样,在与其他材料接触时会产生泛音。因此,可以利用这种现象检查晶圆的质量,即使在生产过程中也是如此。

诺贝尔奖得主Anne l'Huillier表示:“我认为他们要求的成就是我们无法实现的。”

ARCNL研究员Peter Kraus展示了记录芯片材料如何以不同角度散射EUV光的测试设置。“我们可以观察到5到10纳米的结构。”Kraus说。传统的光学计量系统无法看到如此微小的细节。

△用于EUV计量的激光器测试台,利用光波的“泛音”,可以映射芯片上的纳米结构

ARCNL正在研究的另一种方法是光声学:利用短脉冲光产生能够“看到”芯片层的声波。芯片结构正在不断缩小,同时在三维空间中增长,这些信息将变得更加重要。

替代性技术:EUV-FEL

目前ASML的EUV光刻机所采用的是被称为激光等离子体EUV光源(EUV-LPP),但随着半导体制程的持续推进,EUV-LPP也将面临更多的挑战。

作为LPP-EUV技术的替代,近年来,美国、中国、日本等国家的研究机构(相关文章:日本提出EUV光刻新方案:光源功率可降低10倍,成本将大幅降低!)都在研发基于直线电子加速器的自由电子激光技术的EUV光源(EUV-FEL)系统,该技术利用磁铁影响电子,可以产生任何波长的光,并且其光源功率足以同时支持10~20台EUV光刻机。这种方法不仅可以绕过ASML所采用的EUV-LPP技术路线,还可大幅降低EUV光源的系统成本。

ASML在2015年左右也研究了EUV-FEL技术,虽然该技术是有效的,却不符合当前需求。因为粒子加速器体积庞大覆盖了整个建筑物,并不适合当前的晶圆厂。而且,一旦EUV-FEL光源产生故障或需要维护,那么接入该光源的10多条生产线都将面临停机问题。对于大多数的芯片制造商或者晶圆代工厂商来说,如果其在一个地区只建几座晶圆厂,那么也就没有必要用这样的一个重型光源。

据了解,ASML也与美国和日本的研究人员一起认真研究了EUV-FEL技术,但最终还是放弃了。尽管如此,美国初创公司Xlight报告称,它希望在2028年将EUV-FEL光源的原型与ASML机器连接起来。

领导ASML研究部门的Jos Benschop坚信,EUV-LPP是目前产生EUV光源的最具成本效益的方法,尤其是在EUV-LPP光源效率持续提高的情况下。

但对于中国来说,在美国和荷兰将EUV光刻机及相关技术对其禁运的背景之下,成本已经不再是关键问题,EUV-FEL技术可能更适合中国将其商用化。毕竟该技术的有效性已经被ASML等厂商证实。

“带头走路要复杂得多。”ASML前技术总监Martin van den Brink在2015年接受NRC采访时说。“我们最初是光刻领域的追随者。你看到有人在你前面开车,心想如果我跟着那些尾灯走,至少我走的方向是正确的。一旦你超越了你的竞争对手,你就必须确定自己的方向。”

本文来自微信公众号:芯智讯 (ID:icsmart),编辑:芯智讯-浪客剑

相关推荐

ASML的EUV光刻之路还能走多远?

EUV光刻,日本强在哪儿?

EUV光刻的新“救星”

美国退出EUV,ASML的内部思考,中国光刻机的崛起

日本第一台ASML EUV光刻机,下月运抵

ASML:从飞利浦弃儿到光刻之王

ASML:我们有五个EUV光刻机客户

ASML的EUV光刻机,是荷、美、台、韩、欧、日一起造出来的

支持2埃米量产!ASML最新路线图曝光:2030年推出Hyper NA EUV!

ASML:将按计划在年底推出首款High NA EUV光刻机

网址: ASML的EUV光刻之路还能走多远? http://m.xishuta.com/newsview137558.html